### ภาคผนวก ก

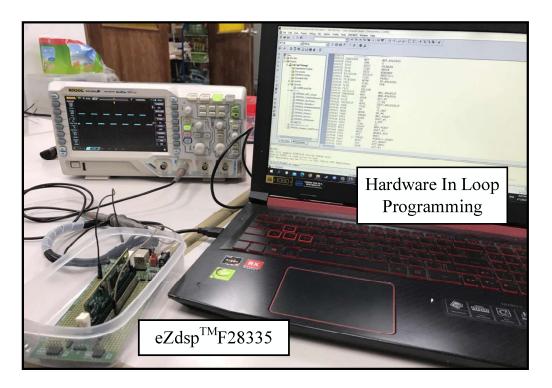

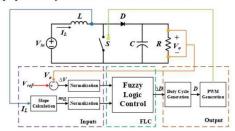

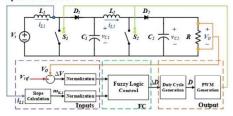

ความรู้พื้นฐานเกี่ยวกับบอร์ดไมโครคอนโทรลเลอร์ DSP รุ่น eZdsp<sup>™</sup>F28335 การควบคุมการทำงานชุดทดสอบวงจรแปลงผันกำลังไฟฟ้าแบบบูสต์เรียงต่อกันสามขั้นนี้ถูก ควบคุมการทำงานด้วยการใช้ตัวควบคุมฟัชซี โดยระบบถูกควบคุมผ่านการเขียนโปรแกรมในภาษาซี เพื่อควบคุมการทำงานผ่านบอร์ดไมโครคอนโทรลเลอร์ โดยที่ได้เลือกใช้บอร์ดไมโครคอนโทรลเลอร์ DSP รุ่น eZdsp™F28335 แสดงได้ในรูปที่ ก.1 สำหรับการประมวลผลในการควบคุม และสร้าง สัญญาณควบคุมการทำงานของสวิตช์ เป็นผลิตภัณฑ์จากบริษัท Texas Instruments โดยมีลักษณะ และส่วนประกอบที่สำคัญดังต่อไปนี้

รูปที่ ก.1 บอร์ดไมโครคอนโทรลเลอร์ DSP รุ่น eZdsp $^{\mathsf{TM}}$ F28335

# คุณสมบัติที่สำคัญของบอร์ดไมโครคอนโทรลเลอร์ DSP รุ่น eZdsp $^{ exttt{TM}}$ F28335

- 1. หน่วยประมวลผลสัญญาณดิจิตอล 32 บิต รองรับการประมวลผลทั้งแบบ floating point unit และ fixed point unit

- 2. ใช้สัญญาณนาฬิกา 150 MHz ในการประมวลผล หรือ 6.67ns ต่อหนึ่งรอบสัญญาณ นาฬิกา

- 3. หน่วยความจำประกอบด้วย

- หน่วยความจำประเภท RAM 68 กิโลไบต์ (68 K bytes on-chip RAM)

- หน่วยความจำประเภท Flash 512 กิโลไบต์ (512 K bytes on-chip Flash memory)

- หน่วยความจำประเภท SRAM 256 กิโลไบต์ (256 K bytes on-chip SRAM memory)

- 4. พอร์ตเชื่อมต่อ XDS100 JTAG Emulator และพอร์ตเชื่อมต่อ RS232 แบบแยกสำหรับ โปรแกรมแบบเวลาจริง (Real-Time in System Programming)

- 5. พอร์ตแปลงสัญญาณแอนาลอกเป็นดิจิตอล (Analog to Digital converter) แบบ 12 บิต จำนวน 16 ช่องสัญญาณอินพุต

- 6. ตัวรับสัญญาณจากเอ็นโค้ดเดอร์ (Quadrature Encoder Pulse) จำนวน 2 ชุด

- 7. ePWM 12 ช่องสัญญาณ (6โมดูล) สำหรับสร้างสัญญาณ PWM

- 8. Serial Peripheral Interface modules SPI จำนวน 1 ชุด (SPI–A)

- 9. Serial Communications Interface modules SCI จำนวน 3 ชุด (SCI-A,SCI-B,SCI-C)

- 10. ขาอินพุต และเอาต์พุตสำหรับเลือกโปรแกรมเพื่อใช้งานจำนวน 96 ขา

### โมดูลการสร้างสัญญาณ PWM (enhanced PWM modules)

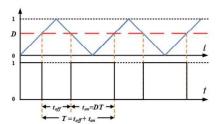

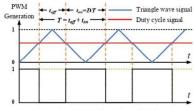

โมดูลการสร้างสัญญาณ PWM ในวงจรสำหรับเปิด–ปิด สวิตช์บนบอร์ดไมโครคอนโทรลเลอร์ DSP รุ่น eZdsp™F28335 ประกอบด้วย ePWM1 – ePWM6 ทั้งหมด 6 ชุด ซึ่งแต่ละชุดสามารถ สร้างได้ 2 ช่อง คือ ePWMxA และ ePWMxB ดังนั้นรวมถึงการสร้างสัญญาณ PWM จำนวน 12 สัญญาณทั้งหมด โดยมีโหมดการนับทั้งหมด 3 โหมด ได้แก่ โหมดนับขึ้น (Count Up mode) โหมด นับลง (Count Down mode) และโหมดการนับขึ้น−ลง (Count Up−Down mode) สำหรับการ สร้างสัญญาณ PWM ของโมคูล ePWM นั้นใช้วิธีการเปรียบเทียบคาวน์เตอร์ (Counter Compare) ของสัญญาณนาฬิกา กับข้อมูล หรือค่าในรีจีสเตอร์เพื่อสร้างเงื่อนไขสำหรับกำหนดรูปแบบสัญญาณ PWM สามารถกำหนดได้ด้วยรีจีสเตอร์ TBPRD (ePWM Period Register) ที่มีขนาด 16 บิต โดย TBPRD จะอยู่ในช่วง 00000 − 65535 โดยมี ความสัมพันธ์กับระบบสัญญาณนาฬิกา 150MHz และรีจีสเตอร์ ปรับค่าสัญญาณนาฬิกา HSPCLKDIV และ CLKDIV ตามสมการ (ก.1) โดยสัญญาณที่ถูกเปรียบเทียบ จากนั้นจะถูกส่งออกผ่านขา GPIO2\_EPWM2A เพื่อให้เกตบอร์ดสวิตช์ได้ทำงานในวงจร อิเล็กทรอนิกส์กำลังต่อไป

$$TBPRF = \frac{1}{2} \left[ \frac{f_{SYSCLKOUT}}{f_{PWM} \left( HSPCLKDIV \times CLKDIV \right)} \right]$$

(n.1)

โดยที่ TBPRD คือ ค่าสูงสุดของตัวนับสัญญาณนาฬิกา

HSPCLKDIV คือ ตัวปรับคูณความเร็วสูงสัญญาณนาฬิกา (High Speed Clock Scalar)

CLKDIV คือ ตัวปรับคูณสัญญาณนาฬิกา (Clock Scalar)

$f_{SYSCLKOUT}$  คือ ความถี่ของระบบสัญญาณนาฬิกา 150MHz

$f_{PWM}$  คือ ความถี่ของสัญญาณ PWM ที่ต้องการสร้าง (Hz)

# การใช้งานโมดูลแปลงสัญญาณแอนาลอกเป็นดิจิตอล ADC (Analog to Digital Converter)

การรับสัญญาณแอนาล็อกจากภายนอกสำหรับบอร์ดไมโครคอนโทรลเลอร์ DSP รุ่น eZdspTMF28335 มีโมดูลที่ใช้ในการแปลงสัญญาณแอนาล็อกเป็นสัญญาณดิจิทัลที่มีความละเอียดที่ ระดับ 12 บิต สำหรับสัญญาณแอนาล็อกที่รองรับ มีแรงดันอยู่ในช่วง 0V ถึง 3V โดยเมื่อบอร์ด ไมโครคอนโทรลเลอร์รับสัญญาณแอนาล็อกที่มีแรงดันดังกล่าว จะทำการแปลงเป็นค่าดิจิทัลที่มีขนาด 12 บิต ซึ่งมีค่าอยู่ระหว่าง 0 – 4095 สำหรับโมดูล ADC มีทั้งหมด 16 ช่องอินพุตสัญญาณ แบ่งเป็น พอร์ตชุด A จำนวน 8 ช่องสัญญาณ (ADCINA0 – ADCINA7) และพอร์ตชุด B จำนวน 8 ช่องสัญญาณ เช่นกัน (ADCINB0 – ADCINB7) ในงานวิจัยนี้ได้เลือกใช้ 3 ช่องสัญญาณ คือ ADCINA1 สำหรับรับ สัญญาณกระแสอินพุต  $i_{L1}$  ที่ไหลผ่านตัวเหนี่ยวนำ  $L_1$  และ ADCINA2 รับสัญญาณแรงดันเอาต์พุตที่ตก คร่อมโหลดในวงจรแปลงผันกำลังไฟฟ้าแบบบุสต์เรียงต่อกันสามขั้น

### ภาคผนวก ข

โปรแกรมภาษาซีสำหรับควบคุมการทำงานชุดทดสอบ

# ข.1 โปรแกรมภาษาซีสร้างสัญญาณ PWM ด้วยบอร์ดไมโครคอนโทรลเลอร์ DSP รุ่น eZdsp™F28335 สำหรับควบคุมแรงดันเอาต์พุตวงจรแปลงผันกำลังไฟฟ้าแบบบูสต์เรียงต่อกันสามขั้น

| สาหรบควบคุมแรงดนเอาตพุตวงจรแบลงผนกาลงเพพ                     | T                                                        |

|--------------------------------------------------------------|----------------------------------------------------------|

| #include "DSP2833x_Device.h"                                 | /โหลด Header file และ Examples Include File              |

| #if (CPU_FRQ_150MHZ)                                         | /กรณี SYSCLKOUT มีค่า 150 MHz                            |

| #define ADC_MODCLK 0x3                                       | /สัญญาณนาฬิกา ADC_HSPCLK = 150/(2*3) = 25MHz             |

| #endif                                                       | /กรณี SYSCLKOUT มีค่า 100 MHz                            |

| #if (CPU_FRQ_100MHZ)                                         | /สัญญาณนาฬิกา ADC_HSPCLK = 100/(2*2) = 25MHz             |

| #define ADC_MODCLK 0x2                                       |                                                          |

| #endif                                                       |                                                          |

| //external function prototypes                               | //ประกาศฟังก์ชันภายนอกใน Header file                     |

| extern void InitAdc(void);                                   | /ฟังก์ชันกำหนดคาพื้นฐานของ ADC                           |

| extern void InitSysCtrl(void);                               | /ฟังก์ชันกำหนดค่าพื้นฐานของ CPU                          |

| extern void InitPieCtrl(void);                               | /ฟังก์ชั่นควบคุม Peripheral Interrupt Expansion          |

| extern void InitPieVectTable(void);                          | /ฟังก์ชันตาราง Peripheral Interrupt Expansion            |

| extern void InitCpuTimers(void);                             | /ฟังก์ชันกำหนดค่าพื้นฐานของ CPU Timer                    |

| extern void ConfigCpuTimer(struct CPUTIMER_VARS *,           | /ฟังก์ชันกำหนดโครงสร้าง CPU Timer                        |

| float, float);                                               |                                                          |

| extern void display_ADC(unsigned int);                       | /ฟังก์ชันกำหนดค่าพื้นฐานของ display ADC                  |

| //Prototype statements for functions found within this file. | //ประกาศฟังก์ซันสำหรับการใช้งาน                          |

| void Gpio_select(void);                                      | /ประกาศฟังก์ชัน Gpio_select                              |

| void Setup_ePWM(void);                                       | /ประกาศฟังก์ชัน Setup_ePWM                               |

| interrupt void cpu_timer0_isr(void);                         | /ประกาศฟังก์ชัน Interrupt cpu_timer0_isr                 |

| interrupt void adc_isr(void);                                | /ประกาศฟังก์ชัน Interrupt adc_isr                        |

| // Global Variables of inputs and outputs                    | ประกาศตัวแปรอิมพุต และเอาต์พุต                           |

| unsigned int Voltage_Vout;                                   | /ประกาศตัวแปรแรงดันเอาต์พุตจากเชนเซอร์                   |

| unsigned int Current_lin;                                    | /ประกาศตัวแปรกระแสอินพุตจากเซนเซอร์                      |

| float vout=0, iin=0, Ts=1e-5, T=0, Trit=1e-4, Vref=400;      | /ประกาศตัวแปรแรงดันเอาต์พุต, กระแสอินพุต, ค่าความถี่การ  |

|                                                              | บันทึกข้อมูล, เวลา คาบของสวิตช์ และแรงดันเอาต์พุตอ้างอิง |

| int duty=3750, ii=0, jj=0;                                   | /ประกาศตัวแปรวัฏจักรหน้าที่สวิตช์, ii และ jj             |

| float Vref=400;                                              | /ประกาศตัวแปรแรงดันเอาต์พุตอ้างอิง                       |

| float Vref1=400, Vref2=400, Vref3=0;                         | /ประกาศตัวแปรแรงดันเอาต์พุตอ้างอิงที่ 1,2 และ 3          |

| float T1=4, T2=8, T3=12;                                     | /ประกาศตัวแปรเวลาที่ 1,2 และ 3                           |

| //Global Averaging Variables                                 | //ประกาศตัวแปรการหาค่าเฉลี่ย                             |

| float iLsum=0;                                               | /ประกาศตัวแปรผลรวมของค่ากระแสอินพุต                      |

| #define AV_S 10                                              | /ประกาศตัวแปร AV_S                                       |

| #define ITdAV 10                                             | /ประกาศตัวแปร ITdAV                                      |

| //Global Fuzzy Controller Variables                          | //ประกาศตัวแปรตัวควบคุมพืชชี                             |

| float dtT=10e-4, mref=160, deltaD=0, pis=0, ss1=0,           | /ประกาศตัวแปรการเปลี่ยนแปลงของเวลา, ความชันอ้างอิง,      |

| iL[10]={0,0,0,0,0,0,0,0,0,0};                                | deltaD, pis, ss1 และ กระแสอินพุตแบบอาเรย์                |

| #define IT_S 100                                             | /ประกาศตัวแปร dtT/Ts                                     |

|                                                              | ,                                                        |

| float VMFs1, VMFs2, VMFs3, mMFs1, mMFs2, mMFs3,                 | /ประกาศตัวแปรฟังก์ชันสมาชิกของ $\Delta V/V_{ref}$                                    |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------|

| mMFs4, mMFs5;                                                   | และ <i>m<sub>il.1</sub></i> /m <sub>ref</sub>                                        |

| float NLmax, NMmax, Zmax, PMmax, PLmax;                         | /ประกาศตัวแปรค่าสูงสุดค่าฟังก์ชันสมาชิกเอาต์พุต                                      |

| float NL=-0.04, NM=-0.02, Z=0, PM=0.02, PL=0.04;<br>//Main Code | /ประกาศตัวแปรฟัชซีของฟังก์ชันสมาชิกของ △D<br>โค้ดหลัก                                |

|                                                                 |                                                                                      |

| InitSysCtrl();                                                  | /เริ่มต้นการทำงานระบบจาก DSP2833x_SysCtrl.c                                          |

| EALLOW;                                                         | /โหลด EALLOW                                                                         |

| SysCtrlRegs.WDCR= 0x00AF;                                       | /โหลด WatchDog                                                                       |

| EDIS;                                                           | /โหลด EDIS                                                                           |

| DINT;                                                           | /หยุดการทำงานของอินเตอร์รัพต์                                                        |

| Gpio_select();                                                  | /กำหนดหน้าที่ของขาอินพุต และเอาต์พุต                                                 |

| Setup_ePWM();                                                   | /กำหนดค่าเริ่มต้นสำหรับ ePWM                                                         |

| InitPieCtrl();                                                  | /กำหนดค่าเริ่มต้นสำหรับ PIE table                                                    |

| InitPieVectTable();                                             | /กำหนดค่าเริ่มต้นสำหรับ ISR's ใน PIE                                                 |

| InitAdc();                                                      | /โหลดค่าเริ่มต้นพื้นฐานของการแปลง ADC                                                |

| AdcRegs.ADCTRL1.all = 0;                                        | /ตั้งค่า AdcRegs.ADCTRL1.all                                                         |

| AdcRegs.ADCTRL1.bit.ACQ_PS = 7;                                 | /ตั้งค่า 7 = 8 x ADCCLK                                                              |

| AdcRegs.ADCTRL1.bit.SEQ_CASC =1;                                | /ตั้งค่า 1=cascaded sequencer                                                        |

| AdcRegs.ADCTRL1.bit.CPS = 0;                                    | /ตั้งค่า divide by 1                                                                 |

| AdcRegs.ADCTRL1.bit.CONT_RUN = 0;                               | /ตั้งค์โหมดแบบ Single Run                                                            |

| AdcRegs.ADCTRL2.all = 0;                                        | /ตั้งค่า AdcRegs.ADCTRL2.all                                                         |

| AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1 = 1;                           | /ตั้งค่า 1=enable SEQ1 interrupt                                                     |

| AdcRegs.ADCTRL2.bit.EPWM_SOCA_SEQ1 =1;                          | /ตั้งค่า 1=SEQ1 start from ePWM_SOCA trigger                                         |

| AdcRegs.ADCTRL2.bit.INT_MOD_SEQ1 = 0;                           | /ตั้งค่า 0= interrupt หลังจากการจบทุกลำดับ                                           |

| AdcRegs.ADCTRL3.bit.ADCCLKPS = 3;                               | /ตั้งค่า ADC clock: FCLK = HSPCLK / 2 * ADCCLKPS                                     |

| AdcRegs.ADCMAXCONV.all = 1;                                     | /กำหนดจำนวนช่องสัญญาณ 1+1= 2 ช่อง                                                    |

| AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0;                            | /กำหนด ADCINA0 as 1st SEQ1 conv.                                                     |

| AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 1;                            | /กำหนด ADCINA1 as 2nd SEQ1 conv.                                                     |

| EPwm6Regs.TBCTL.all = 0xC030;                                   | /Configure timer control register                                                    |

| EPwm6Regs.TBPRD = 2999;                                         | / TPPRD +1 = TPWM / (HSPCLKDIV * CLKDIV *<br>TSYSCLK) โดยที่เท่ากับ 20 µs / 6.667 ns |

| EPwm6Regs.ETPS.all = 0x0100;                                    | /Configure ADC start by ePWM2                                                        |

| EPwm6Regs.ETSEL.all = 0x0A00; EALLOW;                           | / Enable SOCA to ADC                                                                 |

| PieVectTable.TINT0 = &cpu_timer0_isr;                           | /ตั้งค่า PieVectTable.TINT0                                                          |

| PieVectTable.ADCINT = &adc_isr; EDIS;                           | /ตั้งค่า PieVectTable.ADCINT                                                         |

| InitCpuTimers();                                                | /ตั้งค่าเริ่มต้น CPU Timer0, 1 and 2                                                 |

| ConfigCpuTimer(&CpuTimer0,150,10);                              | /ตั้งค่า Sampling time 1e–5=10*1e–6                                                  |

| PieCtrlRegs.PIEIER1.bit.INTx7 = 1;                              | /CPU Timer 0                                                                         |

| PieCtrlRegs.PIEIER1.bit.INTx6 = 1;                              | /ADC                                                                                 |

| IER  =1; EINT; ERTM;                                            |                                                                                      |

| CpuTimer0Regs.TCR.bit.TSS = 0;           | /เริ่มต้น timer0                             |

|------------------------------------------|----------------------------------------------|

| while(1){                                |                                              |

| EALLOW;                                  |                                              |

| SysCtrlRegs.WDKEY = 0x55;                | /Service WD #1                               |

| EDIS;}                                   |                                              |

| }                                        |                                              |

| //Function Gpio_select                   | ฟังก์ชัน Gpio_select                         |

| void Gpio_select(void){                  | /เริ่มต้น void Gpio_select                   |

| EALLOW;                                  |                                              |

| GpioCtrlRegs.GPAMUX1.all = 0;            | /ตั้งค่า GPIO15 GPIO0 = General Puropse I/O  |

| GpioCtrlRegs.GPAMUX1.bit.GPIO0 = 1;      | /ตั้งค่า ePWM1A active == S                  |

| GpioCtrlRegs.GPAMUX2.all = 0;            | /ตั้งค่า GPIO31 GPIO16 = General Purpose I/O |

| GpioCtrlRegs.GPBMUX1.all = 0;            | /ตั้งค่า GPIO47 GPIO32 = General Purpose I/O |

| GpioCtrlRegs.GPBMUX2.all = 0;            | /ตั้งค่า GPIO63 GPIO48 = General Purpose I/O |

| GpioCtrlRegs.GPCMUX1.all = 0;            | /ตั้งค่า GPIO79 GPIO64 = General Purpose I/O |

| GpioCtrlRegs.GPCMUX2.all = 0;            | /ตั้งค่า GPIO87 GPIO80 = General Purpose I/O |

| GpioCtrlRegs.GPADIR.all = 0;             |                                              |

| GpioCtrlRegs.GPBDIR.all = 0;             | /ตั้งค่า GPIO63–32 as inputs                 |

| GpioCtrlRegs.GPCDIR.all = 0; EDIS;       | /ตั้งค่า GPIO87–64 as inputs                 |

| }                                        |                                              |

| //Function Setup_ePWM                    | ฟังก์ชัน Setup_ePWM                          |

| void Setup_ePWM(void){                   | /เริ่มต้น void Setup_ePWM                    |

| EPwm1Regs.TBCTL.all = 0;                 | /default status                              |

| EPwm1Regs.TBCTL.bit.CLKDIV = 0;          | /CLKDIV = 1                                  |

| EPwm1Regs.TBCTL.bit.HSPCLKDIV = 1;       | /HSPCLKDIV = 2                               |

| EPwm1Regs.TBCTL.bit.CTRMODE = 2;         | /up – down mode                              |

| EPwm1Regs.AQCTLA.all = 0x0060;           | /Set ePWM1A on CMPA up                       |

|                                          | Clear ePWM1A on CMPA down                    |

| EPwm1Regs.TBPRD = 3750;                  | /3750=10KHz – PWM signal                     |

| EPwm1Regs.CMPA.half.CMPA = 3750;         | / duty1 => 30%=2625 , 50%=1875 , 70%=1125    |

| }                                        |                                              |

| //Function interrupt void cpu_timer0_isr | ฟังก์ชัน interrupt void cpu_timer0_isr       |

| interrupt void cpu_timer0_isr(void){     | /เริ่มต้น interrupt void cpu_timer0_isr      |

| static int up_down = 1;                  |                                              |

| EALLOW;                                  |                                              |

| SysCtrlRegs.WDKEY = 0xAA;                | /Service WD #2                               |

| if(up_down){                             |                                              |

| if(EPwm1Regs.CMPA.half.CMPA <            |                                              |

| EPwm1Regs.TBPRD)                         |                                              |

| EPwm1Regs.CMPA.half.CMPA;                |                                              |

| else up_down = 0;                        |                                              |

| }else{                                                                                                                                        |                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| if(EPwm1Regs.CMPA.half.CMPA > 0)                                                                                                              |                                                                      |

| EPwm1Regs.CMPA.half.CMPA;                                                                                                                     |                                                                      |

| else up_down = 1;}                                                                                                                            |                                                                      |

| PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;                                                                                                       |                                                                      |

| FUZZYC();                                                                                                                                     | /เรียกฟังก์ชัน FUZZYC                                                |

| T=T+Ts;                                                                                                                                       | /นับเวลา                                                             |

| if(T>T1&&T <t2){vref=vref1;}< td=""><td>/ฟังก์ชัน if สำหรับเปลี่ยนแรงดันเอาต์พุตอ้างอิง</td></t2){vref=vref1;}<>                              | /ฟังก์ชัน if สำหรับเปลี่ยนแรงดันเอาต์พุตอ้างอิง                      |

| if(T>T2&&T <t3){vref=vref2;}< td=""><td></td></t3){vref=vref2;}<>                                                                             |                                                                      |

| if(T>T3){Vref=Vref3;}                                                                                                                         |                                                                      |

| if(vout>500){Vref = 0;                                                                                                                        | /ฟังก์ชันป้องกันเมื่อเอาต์พุตมากกว่า 500V                            |

| EPwm1Regs.CMPA.half.CMPA = 3750;}                                                                                                             |                                                                      |

| if(iin>10){Vref = 0;                                                                                                                          | และกระแสอินพุตมากกว่า 5A                                             |

| EPwm1Regs.CMPA.half.CMPA = 3750;}                                                                                                             |                                                                      |

| //Function interrupt void adc_isr                                                                                                             | ฟังก์ชัน interrupt void adc_isr                                      |

| interrupt void adc_isr(void){                                                                                                                 | /เริ่มต้น interrupt void adc_isr                                     |

| Voltage_Vout = AdcMirror.ADCRESULT0;                                                                                                          | /รับค่าดิจิตอลของแรงดันเอาต์พุต                                      |

| Current_lin = AdcMirror.ADCRESULT1;                                                                                                           | /รับค่าดิจิตอลของกระแสอินพุต                                         |

| AdcRegs.ADCTRL2.bit.RST_SEQ1 = 1                                                                                                              | /Reset SEQ1                                                          |

| AdcRegs.ADCST.bit.INT_SEQ1_CLR = 1;                                                                                                           | /Clear INT SEQ1 bit                                                  |

| PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;                                                                                                       | /Acknowledge interrupt to PIE                                        |

| vout=(0.1223*Voltage_Vout)+1.8988;                                                                                                            | /ปรับเทียบค่าแรงดันเอาต์พุต                                          |

| iin=(0.00274*Current_lin)+0.1698;                                                                                                             | /ปรับเทียบค่ากระแสอินพุต                                             |

| iLsum=iLsum+iin, ii++;                                                                                                                        | /การเก็บสะสมค่ากระแส และการนับค่า ii                                 |

| $if(ii >= AV_S){$                                                                                                                             | /ฟังก์ชันถ้า ii มากกว่า AV_S                                         |

| for(jj=0;jj <itdav-1; jj++){il[jj]="iL[jj+1];}&lt;/td"><td>แล้วฟังก์ชัน For loop สำหรับเลื่อนค่า iL</td></itdav-1;>                           | แล้วฟังก์ชัน For loop สำหรับเลื่อนค่า iL                             |

| iL[ITdAV-1] = iLsum/AV_S;                                                                                                                     | การหาค่าเฉลี่ย iL จาก iLsum/AV_S                                     |

| ii=0, iLsum=0;}                                                                                                                               | การรีเซตค่า ii และ iLsum                                             |

| mdmref=((iL[ITdAV-1]-iL[0])/dtT)/mref/100;                                                                                                    | /คำนวณค่า <i>m<sub>iL1</sub></i> /m <sub>ref</sub>                   |

| }                                                                                                                                             |                                                                      |

| //Function void FUZZYC                                                                                                                        | ฟังก์ชัน Fuzzy Controller                                            |

| void FUZZYC(void){                                                                                                                            | /เริ่มต้น void FUZZYC                                                |

| VMFs1=0, VMFs2=0, VMFs3=0;                                                                                                                    | /กำหนดค่าเริ่มต้นสมาชิกฟังก์ชัน VMFs                                 |

| mMFs1=0, mMFs2=0, mMFs3=0, mMFs4=0, mMFs5=0;                                                                                                  | /กำหนดค่าเริ่มต้นสมาชิกฟังก์ชัน mMFs                                 |

| NLmax=0, NMmax=0, Zmax=0, PMmax=0, PLmax=0;                                                                                                   | /กำหนดค่าเริ่มต้นสมาชิกฟังก์ชันสูงสุด NL NM Z PM และ PL              |

| dVdVref= (Vref-vout)/Vref;                                                                                                                    | /คำนวณค่า <i>∆V/V<sub>ref</sub></i>                                  |

| if(dVdVref>0){VMFs1=0;                                                                                                                        |                                                                      |

| }else if (-Vintv <dvdvref &&="" dvdvref<="0){&lt;/td"><td>/ฟังก์ชันตรวจสอบ <i>∆V/V<sub>ref</sub></i> ในช่วง N เพื่อหาค่า VMFs1</td></dvdvref> | /ฟังก์ชันตรวจสอบ <i>∆V/V<sub>ref</sub></i> ในช่วง N เพื่อหาค่า VMFs1 |

| VMFs1=-(1/Vintv)*dVdVref;                                                                                                                     |                                                                      |

| }else{VMFs1=1;}                                                                                                                               |                                                                      |

| if(dVdVref>Vintv){VMFs2=0;                                                                                                                    | /ฟังก์ชันตรวจสอบ ∆V/V <sub>ref</sub> ในช่วง Z เพื่อหาค่า VMFs2       |

```

}else if (0<dVdVref && dVdVref<=Vintv){

VMFs2=-(1/Vintv)*dVdVref+1;

}else if (-Vintv<dVdVref && dVdVref<=0){

VMFs2=(1/Vintv)*dVdVref+1;

}else{VMFs2=0;}

/ฟังก์ชันตรวจสอบ \Delta V/V_{ref} ในช่วง P เพื่อหาค่า VMFs3

if(dVdVref>Vintv){VMFs3=1:

}else if (0<dVdVref && dVdVref<=Vintv){

VMFs3=(1/Vintv)*dVdVref;

}else{VMFs3=0;}

/ฟังก์ชันตรวจสอบ m_{iL1}/m_{ref} ในช่วง NL เพื่อหาค่า mMFs1

if(mdmref>-1){mMFs1=0};

}else if (-2<mdmref && mdmref<=-1){

mMFs1=-(mdmref)-1;

}else{mMFs1=1;}

/ฟังก์ชันตรวจสอบ m_{i\!L1}\!/m_{r\!e\!f} ในช่วง NM เพื่อหาค่า mMFs2

if(mdmref>0){mMFs2=0;

}else if (-1<mdmref && mdmref<=0){

mMFs2=-(mdmref);

}else if (-2<mdmref && mdmref<=-1){

mMFs2=mdmref+2;

}else{mMFs2=0;}

/ฟังก์ชันตรวจสอบ m_{iL1}/m_{ref} ในช่วง Z เพื่อหาค่า mMFs3

if(mdmref>1){mMFs3=0;

}else if (0<mdmref && mdmref<=1){

mMFs3=-(mdmref)+1;

}else if (-1<mdmref && mdmref<=0){

mMFs3=mdmref+1;

}else{mMFs3=0;}

/ฟังก์ชันตรวจสอบ m_{i\!L1}\!/m_{r\!e\!f} ในช่วง PM เพื่อหาค่า mMFs4

if(mdmref>2){mMFs4=0;

} else if (1<mdmref && mdmref<=2){

mMFs4=-(mdmref)+2;

} else if (0<mdmref && mdmref<=1){

mMFs4=mdmref;

} else{mMFs4=0;}

/ฟังก์ชันตรวจสอบ miL1/mref ในช่วง PL เพื่อหาค่า mMFs5

if(mdmref>2){mMFs5=1};

}else if (1<mdmref && mdmref<=2){

mMFs5=mdmref-1;

}else{mMFs5=0;}

/กฎฟัซซีที่ 6 ถึง 10 กรณี VMFs1 ของ Z มากกว่า 0

if(VMFs1>0){}

/กฎข้อที่ 1 ฟังก์ชันเปรียบเทียบ VMFs1 และ mMFs1 เพื่อให้

if(mMFs1>0){

ได้ค่า PLmax ที่สูงที่สุด

if(VMFs1<mMFs1){

if(PLmax>=VMFs1){PLmax=PLmax;

}else{PLmax=VMFs1;

}else{

if(PLmax>=mMFs1){PLmax=PLmax;

```

```

}else{PLmax=mMFs1;}

}

/กฎข้อที่ 2 ฟังก์ชันเปรียบเทียบ VMFs1 และ mMFs2 เพื่อให้

if(mMFs2>0){

ได้ค่า Zmax ที่สูงที่สุด

if(VMFs1< mMFs2){}

if(Zmax>=VMFs1){Zmax=Zmax;

}else{Zmax=VMFs1;}

}else{

if(Zmax>=mMFs2){Zmax=Zmax;

}else{Zmax=mMFs2;}

}

}

/กฎข้อที่ 3 ฟังก์ชันเปรียบเทียบ VMFs1 และ mMFs3 เพื่อให้

if(mMFs3>0){

ได้ค่า NMmax ที่สูงที่สุด

if(VMFs1<mMFs3){

if(NMmax>=VMFs1){NMmax=NMmax;

}else{NMmax=VMFs1;}

}else{

if(NMmax>=mMFs3){NMmax=NMmax;

}else{NMmax=mMFs3;}

}

/กฎข้อที่ 4 ฟังก์ชันเปรียบเทียบ VMFs1 และ mMFs4 เพื่อให้

if(mMFs4>0){

ได้คา NLmax ที่สูงที่สุด

if(VMFs1< mMFs4){}

if(NLmax>=VMFs1){NLmax=NLmax;

}else{NLmax=VMFs1;}

}else{

if(NLmax>=mMFs4){NLmax=NLmax;

}else{NLmax=mMFs4;}

/กฎข้อที่ 5 ฟังก์ชันเปรียบเทียบ VMFs1 และ mMFs5 เพื่อให้

if(mMFs5>0){

ได้ค่า NLmax ที่สูงที่สุด

if(VMFs1<mMFs5){

if(NLmax>=VMFs1){NLmax=NLmax;}

else{NLmax=VMFs1;}

}else{

if(NLmax>=mMFs5){NLmax=NLmax;

}else{NLmax=mMFs5;}

}

/กฎฟัซซีที่ 6 ถึง 10 กรณี VMFs2 ของ Z มากกว่า 0

if(VMFs2>0){

```

```

/กฎข้อที่ 6 ฟังก์ชันเปรียบเทียบ VMFs2 และ mMFs1 เพื่อให้

if(mMFs1>0){

ได้ค่า PLmax ที่สูงที่สุด

if(VMFs2<mMFs1){

if(PLmax>=VMFs2){PLmax=PLmax;

}else{PLmax=VMFs2;}

}else{

if(PLmax>=mMFs1){PLmax=PLmax;

}else{PLmax=mMFs1;}

}

/กฎข้อที่ 7 ฟังก์ชันเปรียบเทียบ VMFs2 และ mMFs2 เพื่อให้

if(mMFs2>0){

ได้ค่า PMmax ที่สูงที่สุด

if(VMFs2<mMFs2){

if(PMmax>=VMFs2){PMmax=PMmax;}

else{PMmax=VMFs2;}

}else{

if(PMmax>=mMFs2){PMmax=PMmax;

}else{PMmax=mMFs2;}

}

/กฎข้อที่ 8 ฟังก์ชันเปรียบเทียบ VMFs2 และ mMFs3 เพื่อให้

if(mMFs3>0){}

ได้ค่า Zmax ที่สูงที่สุด

if(VMFs2<mMFs3){

if(Zmax>=VMFs2){Zmax=Zmax;

}else{Zmax=VMFs2;}

}else{

if(Zmax>=mMFs3){Zmax=Zmax;

}else{Zmax=mMFs3;}

}

}

/กฎข้อที่ 9 ฟังก์ชันเปรียบเทียบ VMFs2 และ mMFs4 เพื่อให้

if(mMFs4>0){

ได้คา NMmax ที่สูงที่สุด

if(VMFs2<mMFs4){

if(NMmax>=VMFs2){NMmax=NMmax;

}else{NMmax=VMFs2;}

if(NMmax>=mMFs4){NMmax=NMmax;

}else{NMmax=mMFs4;}

/กฎข้อที่ 10 ฟังก์ชันเปรียบเทียบ VMFs2 และ mMFs5 เพื่อให้

if(mMFs5>0){

ได้ค่า NLmax ที่สูงที่สุด

if(VMFs2<mMFs5){

if(NLmax>=VMFs2){NLmax=NLmax;

}else{NLmax=VMFs2;}

}else{

if(NLmax>=mMFs5){NLmax=NLmax;

```

```

}else{NLmax=mMFs5;}

}

}

/กฎฟัซซีที่ 11 ถึง 15 กรณี VMFs3 ของ N มากกว่า 0

if(VMFs3>0){

//กฎข้อที่ 11 ฟังก์ชันเปรียบเทียบ VMFs3 และ mMFs1

if(mMFs1>0){

เพื่อให้ได้ค่า PLmax ที่สูงที่สุด

if(VMFs3<mMFs1){

if(PLmax>=VMFs3){PLmax=PLmax;

}else{PLmax=VMFs3;}

}else{

if(PLmax>=mMFs1){PLmax=PLmax;

}else{PLmax=mMFs1;}

}

}

/กฎข้อที่ 12 ฟังก์ชันเปรียบเทียบ VMFs3 และ mMFs2 เพื่อให้

if(mMFs2>0){

ได้ค่า PLmax ที่สูงที่สุด

if(VMFs3<mMFs2){

if(PLmax>=VMFs3){PLmax=PLmax;

}else{PLmax=VMFs3;}

if(PLmax>=mMFs2){PLmax=PLmax;

}else{PLmax=mMFs2;}

}

/กฎข้อที่ 13 ฟังก์ชันเปรียบเทียบ VMFs3 และ mMFs3 เพื่อให้

if(mMFs3>0){

ได้ค่า PMmax ที่สูงที่สุด

if (VMFs3 < mMFs3) \{\\

if(PMmax>=VMFs3){PMmax=PMmax;

}else{PMmax=VMFs3;}

}else{

if(PMmax>=mMFs3){PMmax=PMmax;

}else{PMmax=mMFs3;}

}

/กฎข้อที่ 14 ฟังก์ชันเปรียบเทียบ VMFs3 และ mMFs4 เพื่อให้

if(mMFs4>0){

ได้ค่า Zmax ที่สูงที่สุด

if(VMFs3<mMFs4){

if(Zmax>=VMFs3){Zmax=Zmax;

}else{Zmax=VMFs3;}

}else{

if(Zmax>=mMFs4){Zmax=Zmax;

}else{Zmax=mMFs4;}

}

```

```

/กฎข้อที่ 15 ฟังก์ชันเปรียบเทียบ VMFs3 และ mMFs5 เพื่อให้

if(mMFs5>0){

ได้ค่า NMmax ที่สูงที่สุด

if(VMFs3<mMFs5){

if(NMmax>=VMFs3){NMmax=NMmax;

}else{NMmax=VMFs3;}

}else{

if(NMmax>=mMFs5){NMmax=NMmax;

}else{NMmax=mMFs5;}

}

}

}

/กระบวนการดีฟัซซีของการอนุมานฟัชซีแบบ Sugeno

deltaD=(NLmax*NL+NMmax*NM+Zmax*Z+PMmax*PM

+PLmax*PL)/(NLmax+NMmax+Zmax+PMmax+PLmax)

*(Ts/Trit);

/คำนวณค่าวัฏจักรหน้าที่สวิตช์ในรูป pis

pis= pis + deltaD;

/แปลง pis เป็นค่าวัฏจักรหน้าที่ duty

duty=3750-(pis*23.4375*5);

/ฟังก์ชันจำกัดช่วง duty 750 ถึง 3750 แล้ว

if(duty>3750){duty=3750;

}else if(duty<750){duty=750;

}else{duty=duty;}

/อัพเดทสัญญาณ PWM ของสวิตช์ทั้งสามตัว

EPwm1Regs.CMPA.half.CMPA = duty;

โดยที่ 30%=2625 , 50%=1875 , 70%=1125

// End of SourceCode.

```

#### ภาคผนวก ค

การจำลองสถานการณ์วงจรแปลงผันกำลังไฟฟ้าแบบบูสต์เรียงต่อกันสามขั้น แบบฮาร์ดแวร์ในลูปที่มีตัวควบคุม และการตรวจจับความผิดพร่องแบบสวิตช์ เปิดวงจร

### เทคนิคการจำลองสถานการณ์แบบฮาร์ดแวร์ในลูป (Hardware In Loop : HIL)

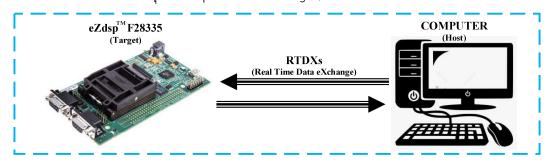

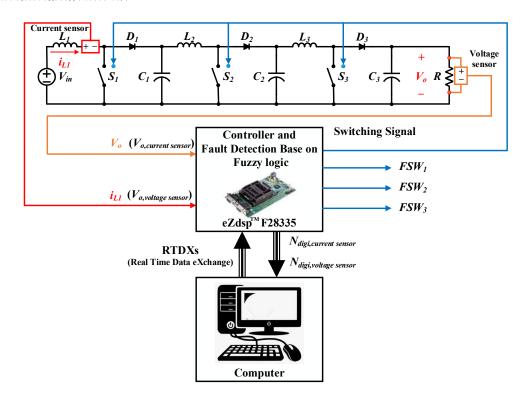

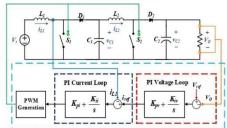

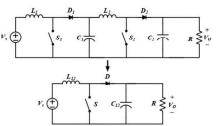

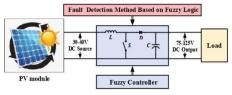

การจำลองสถานการณ์แบบฮาร์ดแวร์ในลูป (Hardware In Loop: HIL) เป็นกระบวนการ ทำงานร่วมกันระหว่างบอร์ดไมโครคอนโทรลเลอร์ DSP รุ่น eZdsp™F28335 และโปรแกรม MATLAB SIMULINK โดยใช้การเขียนคำสั่งควบคุมพีชซีและตัวตรวจจับความผิดพร่องแบบสวิตช์เปิด วงจรที่พัฒนาด้วยภาษาซี และบันทึกลงในบอร์ดไมโครคอนโทรลเลอร์ DSP รุ่น eZdsp™F28335 เพื่อประมวลผล และควบคุมแรงดันเอาต์พุตของวงจรระดับแรงดันแบบหลายอินพุตที่มีอัตราขยาย แรงดันสูงตามที่ต้องการ การจำลองสถานการณ์แบบฮาร์ดแวร์ในลูปใช้พารามิเตอร์ของตัวควบคุมพีช ซี และตัวตรวจจับความผิดพร่องแบบสวิตซ์เปิดวงจรที่ออกแบบตามที่นำเสนอในบทที่ 4 และบทที่ 5 ตามลำดับ บอร์ดไมโครคอนโทรลเลอร์ DSP รุ่น eZdsp™F28335 จะทำหน้าที่ในการประมวลผล ของตัวควบคุมพีไอที่พัฒนาขึ้น เพื่อส่งสัญญาณ PWM และสัญญาการตรวจจับความผิดพร่องแบบ สวิตซ์เปิดวงจรของสวิตซ์กำลังทั้งสามตัวของวงจรแปลงผันกำลังไฟฟ้าแบบบูสต์เรียงต่อกันสามขั้น ที่ อยู่ในโปรแกรม MATLAB SIMULINK และเชื่อมต่อบอร์ดไมโครคอนโทรลเลอร์ DSP รุ่น eZdsp™F28335 กับโปรแกรม MATLAB ผ่านทางพอร์ต USB ตามแผนภาพรูปที่ ค.1 ที่แสดงถึง หลักการทำงานของฮาร์ดแวร์ในลูป ซึ่งเป็นการรับส่งข้อมูลผ่านทางช่องสื่อสารแบบ RTDX (Real Time Data eXchange) เชื่อมโยงโปรแกรม MATLAB SIMULINK (Host) กับบอร์ด ไมโครคอนโทรลเลอร์ DSP รุ่น eZdsp™F28335 (Tarqet)

รูปที่ ค.1 แผนการเชื่อมโยงโปรแกรม SIMULINK กับบอร์ด DSP รุ่น eZdsp $^{\mathsf{TM}}$ F28335

## การเชื่อมโยงซอฟต์แวร์ MATLAB กับบอร์ด $eZdsp^{TM}F28335$

การเชื่อมโยงซอฟต์แวร์กับบอร์ด eZdsp<sup>TM</sup>F28335 จะเริ่มต้นด้วยการติดตั้งซอฟต์แวร์ MATLAB และโปรแกรม F28335 eZdsp CCStudio v3.3 โดยมีไอคอนโปรแกรมเพื่อความสะดวก ดังแสดงในรูปที่ ค.2 ซึ่งประกอบด้วยโปรแกรม MATLAB ที่ใช้สำหรับแก้ไขโปรแกรมควบคุมภาษาซีที่ เขียนขึ้นสำหรับบอร์ด eZdsp<sup>TM</sup>F28335 และโปรแกรม Setup CCStudio  $\lor$ 3.3 ที่ใช้สำหรับกำหนด คุณสมบัติของบอร์ด eZdsp<sup>TM</sup>F28335 ได้อย่างง่ายดาย

รูปที่ ค.2 ไอคอนซอฟต์แวร์โปรแกรมสำหรับการแบบฮาร์ดแวร์ในลูป

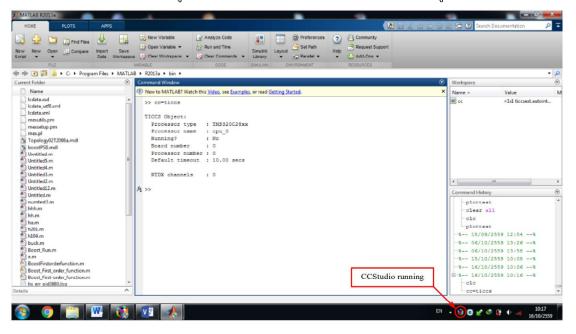

เพื่อเชื่อมต่อโปรแกรม MATLAB กับบอร์ด eZdsp<sup>TM</sup>F28335 สามารถทำได้โดยเชื่อมต่อ บอร์ดเข้ากับคอมพิวเตอร์ผ่านทางพอร์ต USB แล้วเปิดโปรแกรม MATLAB บนหน้าต่าง Command Window หลังจากนั้นให้พิมพ์คำสั่ง "cc=ticcs" เพื่อตรวจสอบว่าบอร์ด eZdsp<sup>TM</sup>F28335 ได้เชื่อมต่อ กับซอฟต์แวร์ MATLAB อย่างถูกต้อง ผลการตรวจสอบจะแสดงบนหน้าต่างดังรูปที่ ค.3

รูปที่ ค.3 การเชื่อมโยงซอฟต์แวร์ MATLAB กับบอร์ด eZdsp $^{\mathsf{TM}}$ F28335

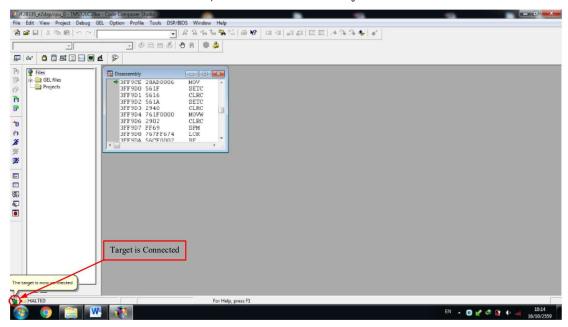

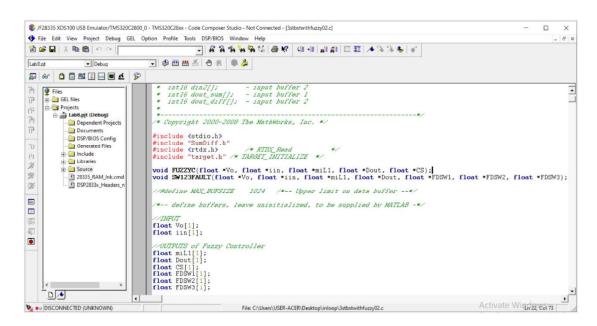

หลังจากนั้นสามารถเปิดโปรแกรม F28335 eZdsp CCStudio v3.3 เพื่อสร้างไฟล์โปรเจกต์ การทำงาน หน้าต่างของโปรแกรม F28335 eZdsp CCStudio v3.3 จะปรากฏอยู่บริเวณมุมล่างซ้าย ของหน้าต่างเช่นที่แสดงในรูปที่ ค.4 หลังจากที่ได้เชื่อมโยงซอฟต์แวร์ MATLAB กับบอร์ด eZdsp<sup>TM</sup>F28335 แล้ว นั่นจะแสดงการเชื่อมต่อบอร์ด eZdsp<sup>TM</sup>F28335 กับโปรแกรม F28335 eZdsp CCStudio v3.3 บนบริเวณมุมล่างซ้ายของหน้าต่างดังรูปที่ ค.4

รูปที่ ค.4 หน้าต่างโปรแกรม F28335 eZdsp CCStudio v3.3

# การเชื่อมโยงโปรแกรม SIMULINK กับบอร์ด eZdsp $^ exttt{TM}$ F28335

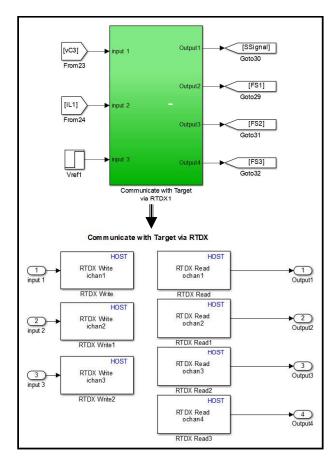

เวลาที่ เชื่อมโยงโปรแกรม SIMULINK กับบอร์ด eZdsp<sup>TM</sup>F28335 เพื่อการจำลอง สถานการณ์แบบฮาร์ดแวร์ในลูป การเชื่อมโยงนี้ประกอบด้วยสองส่วนหลักคือส่วนการรับข้อมูล และ ส่วนการส่งข้อมูลระหว่างโปรแกรม SIMULINK และบอร์ด eZdsp<sup>TM</sup>F28335 ผ่านช่องทางสื่อสาร แบบ RTDX กระบวนการการสื่อสารรับส่งข้อมูลเหล่านี้สามารถแบ่งออกเป็น 4 กรณีหลัก ได้แก่ การ ส่งข้อมูลจากโปรแกรม SIMULINK ไปยังบอร์ด eZdsp<sup>TM</sup>F28335 การรับข้อมูลของโปรแกรม SIMULINK จากบอร์ด eZdsp<sup>TM</sup>F28335 การส่งข้อมูลจากบอร์ด eZdsp<sup>TM</sup>F28335 มายังโปรแกรม SIMULINK และการรับข้อมูลของบอร์ด eZdsp<sup>TM</sup>F28335 จากโปรแกรม SIMULINK แต่ละกรณี สามารถอธิบายได้ดังต่อไปนี้

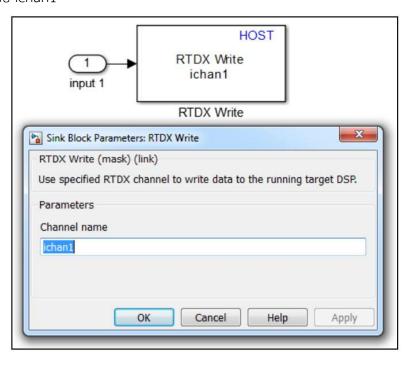

**กรณีที่ 1** การส่งข้อมูลจากโปรแกรม SIMULINK ไปยังบอร์ด eZdsp<sup>TM</sup>F28335 สามารถทำ ได้โดยการใช้บล็อกอินพุต RTDX Write ซึ่งสามารถเรียกใช้ได้จากไลบรารี RTDX simulation block ภายในโปรแกรม MATLAB การกำหนดค่าพารามิเตอร์ของบล็อกอินพุต RTDX Write เพียงแค่ระบุชื่อ ช่องอินพุต (Channel name) เท่านั้น ในที่นี้สามารถใช้ตัวอย่างชื่อช่องอินพุตสำหรับระบบการ ทดสอบการรับ และส่งข้อมูลระหว่างโปรแกรม SIMULINK และบอร์ด eZdsp<sup>TM</sup>F28335 ผ่านทาง

ช่องสื่อสารแบบ RTDX ซึ่งแสดงในรูปที่ ค.5 นี้ เป็นการรับข้อมูลจากโปรแกรม SIMULINK และบันทึก ไว้ในตัวแปรชื่อ ichan1

รูปที่ ค.5 การกำหนดค่าบล็อก RTDX Write

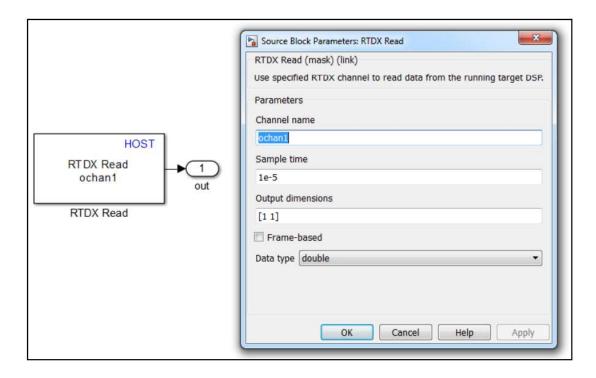

รูปที่ ค.6 การกำหนดค่าบล็อก RTDX Read

กรณีที่ 2 รับข้อมูลจากโปรแกรม SIMULINK มายังบอร์ด eZdsp<sup>TM</sup>F28335 สามารถทำได้ โดยการใช้บล็อกเอาต์พุต RTDX Read ซึ่งอยู่ในไลบรารี RTDX simulation block การกำหนด ค่าพารามิเตอร์ของบล็อกเอาต์พุต RTDX Read รวมถึงชื่อของช่องเอาต์พุต (Channel name) ช่วงเวลาในการซัก (Sample Time) ขนาดของข้อมูลที่ส่งมาจากบอร์ด eZdsp<sup>TM</sup>F28335 (Output dimensions) และชนิดข้อมูล (Data type) สามารถกำหนดได้ตามที่แสดงในรูปที่ ค.6 (double คือ ชนิดข้อมูลแบบตัวเลขทศนิยมละเอียด)

*กรณีที่ 3* การส่งข้อมูลจากบอร์ด eZdsp™F28335 มายังโปรแกรม SIMULINK สามารถทำ ได้โดยใช้ชุดคำสั่งในภาษาซีบนโปรแกรม F28335 eZdsp CCStudio v3.3 ดังนี้:

- RTDX\_CreateOutChannel(ochan1): เป็นฟังก์ชันคำสั่งที่ใช้สร้างช่องเอาต์พุต RTDX เพื่อ ส่งข้อมูลมายังโปรแกรม SIMULINK โดยชื่อของช่องเอาต์พุตนี้จะต้องระบุให้เหมือนกับชื่อ ของช่องการรับข้อมูลของโปรแกรม SIMULINK

- RTDX\_enableOutput(&ochan1): เป็นฟังก์ชันคำสั่งที่เปิดใช้งานช่องเอาต์พุต RTDX ที่มี ชื่อว่า ochan1 เพื่อส่งข้อมูลมายังโปรแกรม SIMULINK

- RTDX\_write(&ochan1,dout1,nbuf\*sizeof(long)): เป็นฟังก์ชันคำสั่งที่ใช้ส่งข้อมูลมายัง โปรแกรม SIMULINK ผ่านทางช่องเอาต์พุต RTDX ที่มีชื่อว่า ochan1 โดยจะต้องระบุค่า ข้อมูล ขนาดของข้อมูล และชนิดข้อมูลในวงเล็บของฟังก์ชันดังกล่าว

*กรณีที่ 4* การรับข้อมูลจากบอร์ด eZdsp™F28335 ไปยังโปรแกรม SIMULINK สามารถทำ ได้โดยใช้ชุดคำสั่งบนโปรแกรม F28335 eZdsp CCStudio  $\lor$ 3.3 ดังนี้:

- ใช้คำสั่ง RTDX\_CreateInputChannel(ichan1) เพื่อสร้างช่องอินพุต RTDX สำหรับรับ ข้อมูลจากโปรแกรม SIMULINK โดยชื่อของช่องอินพุตต้องกำหนดให้ตรงกับชื่อของช่อง เอาต์พุตของโปรแกรม SIMULINK

- ใช้คำสั่ง RTDX\_enableInput(&ichan1) เพื่อเปิดใช้งานช่องอินพุต RTDX ชื่อ ichan1 เพื่อ รับข้อมูลมายังโปรแกรม SIMULINK

- ใช้คำสั่ง RTDX\_read(&ichan1, din1, nbuf\*sizeof(long)) เพื่ออ่านข้อมูลที่รับมาจากช่อง อินพุต RTDX ชื่อ ichan1

เทคนิคการจำลองสถานการณ์แบบฮาร์ดแวร์ในลูปเป็นการจำลองสถานการณ์ที่ใช้บอร์ด eZdsp<sup>TM</sup>F28335 ในการรับส่งข้อมูลระหว่างซอฟต์แวร์ที่เป็นโปรแกรมบนคอมพิวเตอร์กับฮาร์ดแวร์ ที่เป็นบอร์ด eZdspT<sup>MF</sup>28335 ผ่านช่องทางการสื่อสารแบบ RTDX และมีจุดประสงค์เพื่อทำให้การ จำลองสถานการณ์มีความเสมือนจริงขึ้น

# การประยุกต์เทคนิคการจำลองสถานการณ์แบบฮาร์ดแวร์ในลูปโดยอาศัยตัวควบคุม และ การตรวจจับความผิดพร่องที่พัฒนาขึ้น

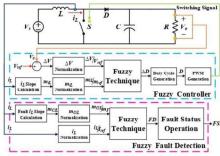

ในกระบวนการจำลองสถานการณ์นี้ จะใช้โปรแกรมควบคุมที่เขียนด้วยภาษาซีที่ถูกพัฒนาขึ้น เพื่อประมวลผลข้อมูลบนบอร์ด eZdsp<sup>TM</sup>F28335 และสื่อสารระหว่างซอฟต์แวร์ MATLAB และ SIMULINK กับระบบฮาร์ดแวร์ผ่านช่องทางการสื่อสาร RTDX โครงสร้างของการจำลองสถานการณ์ แบบฮาร์ดแวร์ในลูปที่ใช้ตัวควบคุม และการตรวจจับความผิดพร่อง โดยอาศัยกระบวนการทางฟัซซี แสดงได้ดังแผนภาพที่ ค.7

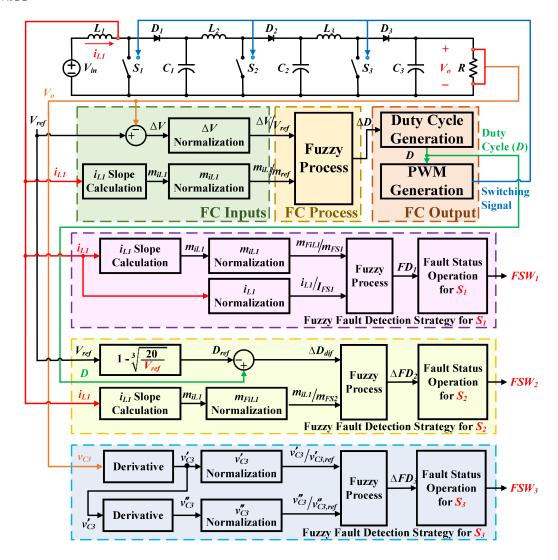

รูปที่ ค.7 โครงสร้างการจำลองสถานการณ์แบบฮาร์ดแวร์ในลูป

จากโครงสร้างการจำลองสถานการณ์แบบฮาร์ดแวร์ในลูปตามแผนภาพที่ ค.7 นี้ เป็น กระบวนการทำงานร่วมกันระหว่างโปรแกรม SIMULINK และบอร์ด eZdspTMF28335 ซึ่งบอร์ดนี้ทำ หน้าที่เป็นตัวควบคุม และตรวจจับความผิดพร่องที่ได้รับการพัฒนาขึ้น โดยสามารถมองเห็น กระบวนการรับส่งข้อมูลระหว่างโปรแกรม SIMULINK และบอร์ด eZdspTMF28335 ในแผนภาพที่ ค. 8 โดยโปรแกรม SIMULINK จะส่งค่าแรงดันเอาต์พุต ( $V_O$ ) และกระแสอินพุตที่ไหลผ่านตัวเหนี่ยวนำ ตัวที่ 1 ( $i_{L1}$ ) ของวงจรแปลงผันกำลังไฟฟ้าแบบบูสต์เรียงต่อกันสามขั้นไปยังบอร์ด และจากนั้นบอร์ด eZdspTMF28335 จะประมวลผลข้อมูลด้วยโปรแกรมภาษาซีที่พัฒนาขึ้นบนโปรแกรม F28335

eZdsp CCStudio v3.3 ตามแสดงในแผนภาพที่ ค.9 จากนั้นบอร์ด eZdsp<sup>TM</sup>F28335 จะส่งสัญญาณ เอาต์พุตเพื่อควบคุมการทำงานของสวิตช์ทั้งสามตัว  $(S_1, S_2$  และ  $S_3$ ) และสัญญาณการตรวจจับ ความผิดพร้อมจะเปิดวงจรของสวิตช์ทั้งสามตัว  $(FS_1, FS_2$  และ  $FS_3$ ) และส่งกลับมายังโปรแกรม SIMULINK

รูปที่ ค.8 แผนภาพระบบ RTDX การรับส่งข้อมูลบนโปรแกรม SIMULINK

การจำลองสถานการณ์แบบฮาร์ดแวร์ในลูปของวงจร สามารถแสดงการเชื่อมต่อระหว่าง คอมพิวเตอร์ที่มีโปรแกรม SIMULINK กับบอร์ด eZdsp™F28335 ได้ดังแสดงในแผนภาพที่ ค.10

รูปที่ ค.9 หน้าต่างโปรแกรม F28335 eZdsp CCStudio v3.3

รูปที่ ค.10 การเชื่อมต่อฮาร์ดแวร์ระหว่างโปรแกรมกับบอร์ด eZdsp $^{\mathsf{TM}}$ F28335

การเขียนโค้ดโปรแกรมภาษาซี โดยกำหนดตัวแปรในการเขียนโปรแกรม และ โครงสร้างการ ทำงานของตัวควบคุม และการตรวจจับความผิดพร่องโดยอาศัยกระบวนการทางฟัซซี แสดงได้ดังรูป ค.11

รูปที่ ค.11 แผนภาพของตัวควบคุม และการตรวจจับความผิดพร่องโดยอาศัยกระบวนการทางฟัซซีใน การเขียนโค้ดโปรแกรมภาษาซี

ค.1 โปรแกรมภาษาซีการจำลองสถานการณ์วงจรแปลงผันกำลังไฟฟ้าแบบบูสต์เรียงต่อกันสามขั้น แบบฮาร์ดแวร์ในลูปที่มีตัวควบคุม และตัวตรวจจับความผิดพร่องแบบสวิตช์เปิดวงจร #include <stdio.h> #include "SumDiff.h" #include <rtdx.h> /\* RTDX\_Read \*/

```

/* TARGET INITIALIZE */

#include "target.h"

void FUZZYC(float *Vo, float *iin, float *miL1, float *Dout, float *CS);

void SW123FAULT(float *Vo, float *iin, float *miL1, float *Dout, float *FDSW1, float *FDSW2,

float *FDSW3):

//#define MAX_BUFSIZE 1024 /*-- Upper limit on data buffer ---*/

/*-- define buffers, leave uninitialized, to be supplied by MATLAB -*/

//INPUT

float Vo[1], iin[1];

//OUTPUTS of Fuzzy Controller

float miL1[1], Dout[1], CS[1], FDSW1[1], FDSW2[1], FDSW3[1];

//Controller Parameters

/* Input parameters */

float Vref=400, Ts=1e-5, dtT=500e-6, mref=160, dVdVref=0, mdmref=0, miin=0;

/* Fuzzy parameters */

float Vintv=10, VMFs1, VMFs2, VMFs3, mMFs1, mMFs2, mMFs3, mMFs4, mMFs5;

PM=0.02, PL=0.04;

/* Output parameters */

float deltaD, Duty=0, ss1;

/* Switching parameters */

float\ Tri\ table [100] = \{0, 0.02, 0.04, 0.06, 0.08, 0.10, 0.12, 0.14, 0.16, 0.18, 0.20, 0.22, 0.24, 0.26, 0.28, 0.30, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20, 0.20

,0.32,0.34,0.36,0.38,0.40,0.42,0.44,0.46,0.48,0.50,0.52,0.54,0.56,0.58,0.60,0.62,0.64,0.66,0.68,0.70,

0.72, 0.74, 0.76, 0.78, 0.80, 0.82, 0.84, 0.86, 0.88, 0.90, 0.92, 0.94, 0.96, 0.98, 1, 0.98, 0.96, 0.94, 0.92, 0.90, 0.88

,0.86,0.84,0.82,0.80,0.78,0.76,0.74,0.72,0.70,0.68,0.66,0.64,0.62,0.60,0.58,0.56,0.54,0.52,0.50,0.48,

0.46, 0.44, 0.42, 0.40, 0.38, 0.36, 0.34, 0.32, 0.30, 0.28, 0.26, 0.24, 0.22, 0.20, 0.18, 0.16, 0.14, 0.12, 0.10, 0.08, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12, 0.12

.06,0.04,0.02}, Trit=1e-4, Triwave=0;

int16 point=0, Tripoint=0;

//Fault Detection for SW1&2&3 Parameters

float dref=0.635, L1=15e-3, Vin=20, Rload=1600, C=500e-6;

//Membership function intervals

/Fault detect SW1

float mFS1=0, iFS1=0, midmf1=0, iLdif=0, mf1MFsN, mf1MFsZ, mf1MFsP, if1MFsPS, if1MFsPM,

if1MFsPL, VNF1=-1, VZF1=0, VPF1=1, NF1, ZF1, PF1, FD1=0, FS1=0;

/MFs of mFiL1/mFS1

```

```

float BB=0.5, AA=0.3;

/MFs of iL1/iFS1

float CC=0.1, DD=0.3, FF=1.7, GG=1.9;

//Fault detect SW2

float dreff2=0, mFS2=0, dduty=0, midmf2=0, FLD2=600, dtMFsN, dtMFsZ, dtMFsP, mf2MFsN,

mf2MFsZ, mf2MFsP, VNF2=-0.05, VZF2=0,VPF2=1, NF2, ZF2, PF2, deltaFD2=0, FD2=0, FS2=0;

/MFs of deltaddif

float HH=0.08, II=0.12;

/MFs of mFiL1/mFS2

float JJ=0.5, KK=1;

//Fault detect SW3

float dv3ref=0, ddv3ref=0, dv3=0, ddv3=0, dv3in=0, ddv3in=0, FLD3=50, dv3MFsPS, dv3MFsPM,

dv3MFsPL, ddv3MFsPS, ddv3MFsPM, ddv3MFsPL, VNF3=-0.05, VZF3=0, VPF3=1, NF3, ZF3, PF3;

float deltaFD3=0, FD3=0, FS3=0;

/MFs of dvc3/dvc3ref

float LL=0.1, MM=0.2, NN=1.8, OO=1.9;

/MFs of ddvc3/ddvc3ref

float PP=0.3, QQ=0.4, RR=1.8, SS=2.5;

/*-- defines actual size, must be less than limit -*/

/*-- defines RTDX channels -*/

RTDX CreateInputChannel (ichan1);

/* Channel from which to receive filter input */

RTDX CreateInputChannel (ichan2);

/* Channel from which to receive filter input */

RTDX CreateOutputChannel(ochan1);

/* Channel to output coefficient updates */

RTDX CreateOutputChannel(ochan2);

/* Channel to output coefficient updates */

/* Channel to output coefficient updates */

RTDX CreateOutputChannel(ochan3);

RTDX CreateOutputChannel(ochan4);

/* Channel to output coefficient updates */

RTDX CreateOutputChannel(ochan5);

/* Channel to output coefficient updates */

RTDX CreateOutputChannel(ochan6);

/* Channel to output coefficient updates */

/*____ main --

void main(){

TARGET INITIALIZE();

/* Target-specific initialization */

/* Enable channels */

RTDX enableInput (&ichan1);

RTDX enableInput (&ichan2);

RTDX enableOutput(&ochan1);

RTDX enableOutput(&ochan2);

RTDX enableOutput(&ochan3);

```

```

RTDX enableOutput(&ochan4);

RTDX_enableOutput(&ochan5);

RTDX enableOutput(&ochan6);

while (1) {

/* Read inputs from host */

RTDX read(&ichan1, Vo, 1 * sizeof(long));

RTDX read(&ichan2, iin, 1 * sizeof(long));

/* Call function */

FUZZYC(Vo, iin, miL1, Dout, CS);

SW123FAULT(Vo, iin, miL1, Dout, FDSW1, FDSW2, FDSW3);

/* Write outputs to host */

while ( RTDX writing != NULL ){ /* wait for previous write to complete */

#if RTDX POLLING IMPLEMENTATION

RTDX Poll();

#endif}

RTDX write( &ochan1, miL1, 1 * sizeof(long));

while ( RTDX writing != NULL ){ /* wait for previous write to complete */

#if RTDX POLLING IMPLEMENTATION

RTDX Poll();

#endif}

RTDX_write( &ochan2, Dout, 1 * sizeof(long) );

while ( RTDX writing != NULL ){ /* wait for previous write to complete */

#if RTDX POLLING IMPLEMENTATION

RTDX Poll();

#endif}

RTDX write( &ochan3, CS, 1 * sizeof(long) );

while ( RTDX_writing != NULL ){ /* wait for previous write to complete */

#if RTDX POLLING IMPLEMENTATION

RTDX Poll();

#endif}

RTDX write( &ochan4, FDSW1, 1 * sizeof(long));

while ( RTDX writing != NULL ){ /* wait for previous write to complete */

#if RTDX POLLING IMPLEMENTATION

RTDX Poll();

#endif}

RTDX_write( &ochan5, FDSW2, 1 * sizeof(long));

```

```

while (RTDX writing != NULL){ /* wait for previous write to complete */

#if RTDX_POLLING_IMPLEMENTATION

RTDX Poll();

#endif}

RTDX write( &ochan6, FDSW3, 1 * sizeof(long));

----- add_sub_buffers ----*/

void FUZZYC(float *Vo, float *iin, float *miL1, float *Dout, float *CS){

short t, ij;

/set zero innitial membership fuction

VMFs1=0, VMFs2=0, VMFs3=0, mMFs1=0, mMFs2=0, mMFs3=0, mMFs4=0, mMFs5=0;

/innitial for find maximum value

NLmax=0, NMmax=0, Zmax=0, PMmax=0, PLmax=0;

for (t = 0; t < 1; t++) {

/ set iL parameter in array

for(ij=0; ij < 50-1; ij++){iL[ij]=iL[ij+1];}

iL[50-1] = iin[t];

/Fuzzy input calculation

dVdVref= (Vref-Vo[t])/Vref;

miin=(iin[t]-iL[0])/dtT;

miL1[t]=miin;

mdmref= miin/mref;

//Check voltage membership function

if(dVdVref>0){VMFs1=0;} /Check if dVdVref is in N interval

else if (-Vintv<dVdVref && dVdVref<=0){VMFs1=-(1/Vintv)*dVdVref;}

else{VMFs1=1;}

if(dVdVref>Vintv){VMFs1=0;}

/Check if dVdVref is in Z interval

else if (0<dVdVref && dVdVref<=Vintv){VMFs2=-(1/Vintv)*dVdVref+1;}

else if (-Vintv<dVdVref && dVdVref<=0){VMFs2=(1/Vintv)*dVdVref+1;}

else{VMFs2=0;}

if(dVdVref>Vintv){VMFs3=1;}

/Check if dVdVref is in P interval

else if (0<dVdVref && dVdVref<=Vintv){VMFs3=(1/Vintv)*dVdVref;}

else{VMFs3=0;}

//Check current slope membership function

if(mdmref>-1)\{mMFs1=0;\}

/Check if mdmref is in NL interval

```

```

else if (-2<mdmref && mdmref<=-1){mMFs1=-(mdmref)-1;}

else{mMFs1=1;}

if(mdmref>0){mMFs2=0;} /Check if mdmref is in NM interval

else if (-1<mdmref && mdmref<=0){mMFs2=-(mdmref):}

else if (-2<mdmref && mdmref<=-1){mMFs2=mdmref+2;}

else{mMFs2=0;}

if(mdmref>1){mMFs3=0;} /Check if mdmref is in Z interval

else if (0<mdmref && mdmref<=1){mMFs3=-(mdmref)+1;}

else if (-1<mdmref && mdmref<=0){mMFs3=mdmref+1;}

else{mMFs3=0;}

if(mdmref>2){mMFs4=0;} /Check if mdmref is in PM interval

else if (1<mdmref && mdmref<=2){mMFs4=-(mdmref)+2;}

else if (0<mdmref && mdmref<=1){mMFs4=mdmref;}

else{mMFs4=0;}

if(mdmref>2){mMFs5=1;} /Check if mdmref is in PL interval

else if (1<mdmref && mdmref<=2){mMFs5=mdmref-1;}

else{mMFs5=0;}

//Check Rule bases 1–15

if(VMFs1>0){

/Rule bases 1–5 VMFs of N >0

if(mMFs1>0){

/1st Rule base

if(VMFs1<mMFs1){

if(PLmax>=VMFs1){PLmax=PLmax;}

else{PLmax=VMFs1;}

}else{

if(PLmax>=mMFs1){PLmax=PLmax;}

else{PLmax=mMFs1;}

}

}

if(mMFs2>0){

/ 2nd Rule base

if(VMFs1<mMFs2){

if(Zmax>=VMFs1){Zmax=Zmax;}

else{Zmax=VMFs1;}

}else{

if(Zmax>=mMFs2){Zmax=Zmax;}

else{Zmax=mMFs2;}

}

```

```

if(mMFs3>0){

/ 3rd Rule base

if(VMFs1<mMFs3){

if(NMmax>=VMFs1){NMmax=NMmax;}

else{NMmax=VMFs1;}

}else{

if(NMmax>=mMFs3){NMmax=NMmax;}

else{NMmax=mMFs3;}

}

}

if(mMFs4>0){

/ 4th Rule base

if(VMFs1<mMFs4){

if(NLmax>=VMFs1){NLmax=NLmax;}

else{NLmax=VMFs1;}

}else{

if(NLmax>=mMFs4){NLmax=NLmax;}

else{NLmax=mMFs4;}

}

}

if(mMFs5>0){

/ 5th Rule base

if(VMFs1<mMFs5){

if(NLmax>=VMFs1){NLmax=NLmax;}

else{NLmax=VMFs1;}

}else{

if(NLmax>=mMFs5){NLmax=NLmax;}

else{NLmax=mMFs5;}

}

}

}

if(VMFs2>0){

/ Rule bases 6–10 VMFs of Z > 0

if(mMFs1>0){

/ 6th Rule base

if(VMFs2<mMFs1){

if(PLmax>=VMFs2){PLmax=PLmax;}

else{PLmax=VMFs2;}

}else{

if(PLmax>=mMFs1){PLmax=PLmax;}

```

```

else{PLmax=mMFs1;}

}

}

if(mMFs2>0){

/7th Rule base

if(VMFs2<mMFs2){

if(PMmax>=VMFs2){PMmax=PMmax;}

else{PMmax=VMFs2;}

}else{

if(PMmax>=mMFs2){PMmax=PMmax;}

else{PMmax=mMFs2;}

}

}

if(mMFs3>0){

/ 8th Rule base

if(VMFs2<mMFs3){

if(Zmax>=VMFs2){Zmax=Zmax;}

else{Zmax=VMFs2;}

}else{

if(Zmax>=mMFs3){Zmax=Zmax;}

else{Zmax=mMFs3;}

}

}

if(mMFs4>0){

/ 9th Rule base

if(VMFs2<mMFs4){

if(NMmax>=VMFs2){NMmax=NMmax;}

else{NMmax=VMFs2;}

}else{

if(NMmax>=mMFs4){NMmax=NMmax;}

else{NMmax=mMFs4;}

}

}

if(mMFs5>0){

/ 10th Rule base

if(VMFs2<mMFs5){

if(NLmax>=VMFs2){NLmax=NLmax;}

else{NLmax=VMFs2;}

}else{

if(NLmax>=mMFs5){NLmax=NLmax;}

```

```

else{NLmax=mMFs5;}

}

}

}

if(VMFs3>0){

/ Rule bases 11-15 VMFs of P >0

if(mMFs1>0){

/ 11th Rule base

if(VMFs3<mMFs1){

if(PLmax>=VMFs3){PLmax=PLmax;}

else{PLmax=VMFs3;}

}else{

if(PLmax>=mMFs1){PLmax=PLmax;}

else{PLmax=mMFs1;}

}

}

if(mMFs2>0){

/ 12th Rule base

if(VMFs3<mMFs2){

if(PLmax>=VMFs3){PLmax=PLmax;}

else{PLmax=VMFs3;}

}else{

if(PLmax>=mMFs2){PLmax=PLmax;}

else{PLmax=mMFs2;}

}

}

if(mMFs3>0){

/ 13th Rule base

if(VMFs3<mMFs3){

if(PMmax>=VMFs3){PMmax=PMmax;}

else{PMmax=VMFs3;}

}else{

if(PLmax>=mMFs3){PLmax=PLmax;}

else{PLmax=mMFs3;}

}

if(mMFs4>0){

/ 14th Rule base

if(VMFs3<mMFs4){

if(Zmax>=VMFs3){Zmax=Zmax;}

else{Zmax=VMFs3;}

```

```

}else{

if(Zmax > = mMFs4){Zmax = Zmax;}

else{Zmax=mMFs4;}

}

}

if(mMFs5>0){

/ 15th Rule base

if(VMFs3<mMFs5){

//ANM[iNM]=VMFs[2];

if(NMmax>=VMFs3){NMmax=NMmax;}

else{NMmax=VMFs3;}

}else{

//ANM[iNM]=mMFs[4];

if(NMmax>=mMFs5){NMmax=NMmax;}

else{NMmax=mMFs5;}

}

}

}

// Defuzzification by Sugeno fuzzy interference

deltaD=(NLmax*NL+NMmax*NM+Zmax*Z+PMmax*PM+PLmax*PL)/(NLmax+NMmax+Z

max+PMmax+PLmax)*(Ts/Trit);

Duty=Duty+deltaD;

// Duty cycle

if(Duty>=1){Duty=1;}

// Saturation

else if(0<=Duty<1){Duty=Duty;}

else{Duty=0;}

Dout[t] = Duty;

point=point+10; //PWM method

if(point >= 100){point = 0;}

Tripoint=point;

Triwave=Tri table[Tripoint];

if(Duty>=Triwave){ss1=1;}

else{ss1=0;}

CS[t] = ss1;

}return;

– Fault Tolerance –––––

```

```

void SW1 23 FAULT(float *Vo, float *iin, float *miL1, float *Dout, float *FDSW1, float *FDSW2,

float *FDSW3){

short t, im, in;

// Fault SW1

/ set zero innitial membership fuction

mf1MFsN=0, mf1MFsZ=0, mf1MFsP=0, if1MFsPS=0, if1MFsPM=0, if1MFsPL=0;

/innitial for find maximum value

NF1=0, ZF1=0, PF1=0;

// Fault SW2

/set zero innitial membership fuction

dtMFsN=0, dtMFsZ=0, dtMFsP=0, mf2MFsN=0, mf2MFsZ=0, mf2MFsP=0;

/innitial for find maximum value

NF2=0, ZF2=0, PF2=0;

// Fault SW3

/set zero innitial membership fuction

dv3MFsPS=0, dv3MFsPM=0, dv3MFsPL=0, ddv3MFsPS=0, ddv3MFsPM=0, ddv3MFsPL=0;

/innitial for find maximum value

NF3=0, ZF3=0, PF3=0;

for (t = 0; t < 1; t++) {

// Fault SW1

mFS1=-Vin*dref/(L1*(1-dref));

iFS1=Vref/(Rload*(1-dref)*(1-dref)*(1-dref));

midmf1=miL1[t]/mFS1;

iLdif=iin[t]/iFS1;

// Check voltage membership function

if(midmf1 <= -BB){mf1MFsN=1;} / Check if midmf1 is in N interval

else if (midmf1 > -BB \&\& midmf1 <= -AA)\{mf1MFsN=(midmf1+AA)*(AA-BB);\}

else{mf1MFsN=0;}

if(midmf1 \le -BB)\{mf1MFsZ=0;\} /Check if midmf1 is in Z interval

else if (midmf1 > -BB \&\& midmf1 <= -AA)\{mf1MFsZ=(midmf1+BB)*(BB-AA);\}

else if (midmf1 > -AA \&\& midmf1 <= AA)\{mf1MFsZ=1;\}

else if (midmf1 > AA && midmf1 <= BB){mf1MFsZ=(midmf1-BB)*(AA-BB);}

else{mf1MFsZ=0;}

if(midmf1 <= AA){mf1MFsP=0;} /Check if midmf1 is in P interval

else if (midmf1 > AA && midmf1 <= BB){mf1MFsP=(midmf1-AA)*(BB-AA);}

else{mf1MFsP=1;}

```

```

if(iLdif <= CC){if1MFsPS=1;} /Check if iLdif is in PS interval

else if (iLdif > CC && iLdif <= DD){if1MFsPS=(iLdif-DD)*(CC-DD);}

else{if1MFsPS=0;}

if(iLdif <= CC){if1MFsPM=0;}

/Check if iLdif is in PM interval

else if (iLdif > CC && iLdif <= DD){if1MFsPM=(iLdif-CC)*(DD-CC);}

else if (iLdif > DD && iLdif <= FF){if1MFsPM=1;}

else if (iLdif > FF && iLdif <= GG){if1MFsPM=(iLdif-GG)*(FF-GG);}

else{if1MFsPM=0;}

if(iLdif <= FF){if1MFsPL=0;}

/Check if iLdif is in PL interval

else if (iLdif > FF && iLdif <= GG){if1MFsPL=(iLdif-FF)*(GG-FF);}

else{if1MFsPL=1;}

// Check Rule bases 1–9

if(mf1MFsN>0){ /Rule bases 1-3 mf1MFsN >0

if(if1MFsPS>0){ / 1st Rule base

if(mf1MFsN<if1MFsPS){

if(PF1>=mf1MFsN){PF1=PF1;}

else{PF1=mf1MFsN;}

}else{

if(PF1>=if1MFsPS){PF1=PF1;}

else{PF1=if1MFsPS;}

}

}

if(if1MFsPM>0){ / 2nd Rule base

if(mf1MFsN<if1MFsPM){</pre>

if(ZF1>=mf1MFsN){ZF1=ZF1;}

else{ZF1=mf1MFsN;}

}else{

if(ZF1>=if1MFsPM){ZF1=ZF1;}

else{ZF1=if1MFsPM;}

}

if(if1MFsPL>0){ / 3rd Rule base

if(mf1MFsN<if1MFsPL){

if(ZF1>=mf1MFsN){ZF1=ZF1;}

else{ZF1=mf1MFsN;}

}else{

```

```

if(ZF1>=if1MFsPL){ZF1=ZF1;}

else{ZF1=if1MFsPL;}

}

}

}

if(mf1MFsZ>0){ / Rule bases 4-6 mf1MFsZ >0

if(if1MFsPS>0){ / 4th Rule base

if(mf1MFsZ<if1MFsPS){

if(PF1>=mf1MFsZ){PF1=PF1;}

else{PF1=mf1MFsZ;}

}else{

if(PF1>=if1MFsPS){PF1=PF1;}

else{PF1=if1MFsPS;}

}

}

if(if1MFsPM>0){ / 5th Rule base

if(mf1MFsZ<if1MFsPM){</pre>

if(ZF1>=mf1MFsZ){ZF1=ZF1;}

else{ZF1=mf1MFsZ;}

}else{

if(ZF1>=if1MFsPM){ZF1=ZF1;}

else{ZF1=if1MFsPM;}

}

if(if1MFsPL>0){ / 6th Rule base

if(mf1MFsZ<if1MFsPL){</pre>

if(ZF1>=mf1MFsZ){ZF1=ZF1;}

else{ZF1=mf1MFsZ;}

}else{

if(ZF1>=if1MFsPL){ZF1=ZF1;}

else{ZF1=if1MFsPL;}

}

}

}

if(mf1MFsP>0){ / Rule bases 7-9 mf1MFsP >0

if(if1MFsPS>0){ / 7th Rule base

```

```

if(mf1MFsP<if1MFsPS){

if(ZF1>=mf1MFsP){ZF1=ZF1;}

else{ZF1=mf1MFsP;}

}else{

if(PF1>=if1MFsPS){ZF1=ZF1;}

else{PF1=if1MFsPS;}

}

}

if(if1MFsPM>0){ / 8th Rule base

if(mf1MFsP<if1MFsPM){</pre>

if(ZF1>=mf1MFsP){ZF1=ZF1;}

else{ZF1=mf1MFsP;}

}else{

if(ZF1>=if1MFsPM){ZF1=ZF1;}

else{ZF1=if1MFsPM;}

}

}

if(if1MFsPL>0){ / 9th Rule base

if(mf1MFsP<if1MFsPL){</pre>

if(NF1>=mf1MFsP){NF1=NF1;}

else{NF1=mf1MFsP;}

}else{

if(NF1>=if1MFsPL){NF1=NF1;}

else{NF1=if1MFsPL;}

}

}

FD1=(NF1*VNF1+ZF1*VZF1+PF1*VPF1)/(NF1+ZF1+PF1);

if(FD1>0.8 && FS2==0 && FS3==0){FS1=1;}

else{FS1=0;}

// Fault SW2

dreff2=pow(Vin/Vref,1/3);

mFS2=2*mref;

dduty=Dout[t]-dreff2;

midmf2=miL1[t]/mFS2;

```

```

// Check voltage membership function dtMFs, mf2MFs

if(dduty \le -II){dtMFsN=1;}

/ Check if dduty is in N interval

else if (dduty > -II && dduty <= -HH){dtMFsN=(dduty+HH)*(HH-II);}

else{dtMFsN=0;}

if(dduty \le -II){dtMFsZ=0;}

/ Check if dduty is in Z interval

else if (dduty > -II && dduty <= -HH){dtMFsZ=(dduty+II)*(II-HH);}

else if (dduty > -HH && dduty <= HH){dtMFsZ=1;}

else if (dduty > HH && dduty <= II){dtMFsZ=(dduty-II)*(HH-II);}

else{dtMFsZ=0;}

if(dduty <= HH){dtMFsP=0;}

/ Check if dduty is in P interval

else if (dduty > HH && dduty <= II){dtMFsP=(dduty-HH)*(II-HH);}

else{dtMFsP=1;}

if(midmf2 <= -KK){mf2MFsN=1;} / Check if midmf2 is in N interval

else if (midmf2 > -KK && midmf2 <= -JJ){mf2MFsN=(midmf2+JJ)*(JJ-KK);}

else{mf2MFsN=0;}

if(midmf2 \leftarrow -KK){mf2MFsZ=0;} /Check if midmf2 is in Z interval

else if (midmf2 > -KK \&\& midmf2 <= -JJ)\{mf2MFsZ=(midmf2+KK)*(KK-JJ);\}

else if (midmf2 > -JJ \&\& midmf2 <= JJ)\{mf2MFsZ=1;\}

else if (midmf2 > JJ && midmf2 <= KK){mf2MFsZ=(midmf2-KK)*(JJ-KK);}

else{mf2MFsZ=0;}

if(midmf2 \le JJ)\{mf2MFsP=0;\}

/ Check if midmf2 is in P interval

else if (midmf2 > JJ && midmf2 <= KK){mf2MFsP=(midmf2-JJ)*(KK-JJ);}

else{mf2MFsP=1;}

// Check Rule bases 1–9

if(dtMFsN>0){ / Rule bases 1-3 dtMFsN >0

if(mf2MFsN>0){ / 1st Rule base

if(dtMFsN<mf2MFsN){

if(ZF2 > = dtMFsN){ZF2 = ZF2;}

else{ZF2=dtMFsN;}

}else{

if(ZF2 >= mf2MFsN){ZF2 = ZF2;}

else{ZF2=mf2MFsN;}

}

}

if(mf2MFsZ>0){ / 2nd Rule base

if(dtMFsN<mf2MFsZ){

```

```

if(NF2>=dtMFsN){NF2=NF2;}

else{NF2=dtMFsN;}

}else{

if(NF2>=mf2MFsZ){NF2=NF2;}

else{NF2=mf2MFsZ;}

}

if(mf2MFsP>0){ / 3rd Rule base

if(dtMFsN<mf2MFsP){

if(ZF2 > = dtMFsN){ZF2 = ZF2;}

else{ZF2=dtMFsN;}

}else{

if(ZF2 >= mf2MFsP){ZF2 = ZF2;}

else{ZF2=mf2MFsP;}

}

}

}

/ Rule bases 4–6 dtMFsZ >0

if(dtMFsZ>0){

if(mf2MFsN>0){ / 4th Rule base

if(dtMFsZ<mf2MFsN){

if(ZF2 >= dtMFsZ){ZF2 = ZF2;}

else{ZF2=dtMFsZ;}

}else{

if(ZF2 \ge mf2MFsN){ZF2 = ZF2;}

else{ZF2=mf2MFsN;}

}

}

if(mf2MFsZ>0){ / 5th Rule base

if(dtMFsZ<mf2MFsZ){

if(NF2>=dtMFsZ){NF2=NF2;}

else{NF2=dtMFsZ;}

}else{

if(NF2>=mf2MFsZ){NF2=NF2;}

else{NF2=mf2MFsZ;}

}

}

```

```

if(mf2MFsP>0){ / 6th Rule base

if(dtMFsZ<mf2MFsP){

if(ZF2 >= dtMFsZ)\{ZF2 = ZF2;\}

else{ZF2=dtMFsZ;}

}else{

if(ZF2 \ge mf2MFsP)\{ZF2 = ZF2;\}

else{ZF2=mf2MFsP;}

}

}

}

if(dtMFsP>0){

/ Rule bases 7–9 dtMFsP >0

if(mf2MFsN>0){ / 7th Rule base

if(dtMFsP<mf2MFsN){

if(PF2>=dtMFsP){PF2=PF2;}

else{PF2=dtMFsP;}

}else{

if(PF2>=mf2MFsN){PF2=PF2;}

else{PF2=mf2MFsN;}

}

if(mf2MFsZ>0){ / 8th Rule base

if(dtMFsP<mf2MFsZ){

if(ZF2 >= dtMFsP)\{ZF2 = ZF2;\}

else{ZF2=dtMFsP;}

}else{

if(ZF2 >= mf2MFsZ)\{ZF2 = ZF2;\}

else{ZF2=mf2MFsZ;}

}

if(mf2MFsP>0){ / 9th Rule base

if(dtMFsP<mf2MFsP){

if(PF2>=dtMFsP){PF2=PF2;}

else{PF2=dtMFsP;}

}else{

if(PF2>=mf2MFsP){PF2=PF2;}

else{PF2=mf2MFsP;}

```

```

}

}

}

deltaFD2=(NF2*VNF2+ZF2*VZF2+PF2*VPF2)/(NF2+ZF2+PF2):

FD2=FD2+deltaFD2;

if(FD2 < 0){FD2=0;}

if(FD2/FLD2 > 1 \&\& FS1==0 \&\& FS3==0){FS2=1;}

else{FS2=0;}

// Fault SW3

dv3ref=-Vref/(Rload*C);

ddv3ref=Vref/((Rload*C)*(Rload*C));

for(im=0; im< 10-1; im++){vC3[im]=vC3[im+1];}

VC3[10-1] = Vo[t];

dv3=(Vo[t]-vC3[0])/(dtT/10);

for(in=0; in< 10-1; in++){difvC3[in]=difvC3[in+1];}

difvC3[10-1]=dv3;

ddv3=(difvC3[10-1]-difvC3[0])/(dtT/10);;

dv3in=dv3/dv3ref;

ddv3in=ddv3/ddv3ref;

// Check voltage membership function dv3MFs, ddv3MFs

if(dv3in <= LL){dv3MFsPS=1;} / Check if dv3in is in PS interval

else if (dv3in > LL \&\& dv3in <= MM){dv3MFsPS=(dv3in-MM)*(LL-MM);}

else{dv3MFsPS=0;}

if(dv3in <= LL){dv3MFsPM=0;} / Check if dv3in is in PM interval

else if (dv3in > LL &\& dv3in <= MM){dv3MFsPM=(dv3in-LL)*(MM-LL);}

else if (dv3in > MM && dv3in <= NN){dv3MFsPM=1;}

else if (dv3in > NN && dv3in <= OO){dv3MFsPM=(dv3in-OO)*(NN-OO);}

else{dv3MFsPM=0;}

if(dv3in <= NN){dv3MFsPL=0;} / Check if dv3in is in PL interval

else if (dv3in > NN && dv3in <= OO){dv3MFsPL=(dv3in-NN)*(OO-NN);}

else{dv3MFsPL=1;}

if(ddv3in <= PP){ddv3MFsPS=1;} / Check if dv3in is in PS interval

else if (ddv3in > PP && ddv3in <= QQ){ddv3MFsPS=(ddv3in-QQ)*(PP-QQ);}

else{ddv3MFsPS=0;}

if(ddv3in <= PP){ddv3MFsPM=0;} / Check if dv3in is in PM interval

```

```

else if (ddv3in > PP && ddv3in <= QQ){ddv3MFsPM=(ddv3in-PP)*(QQ-PP);}

else if (ddv3in > QQ && ddv3in <= RR){ddv3MFsPM=1;}

else if (ddv3in > RR && ddv3in <= SS){ddv3MFsPM=(ddv3in-SS)*(RR-SS);}

else{ddv3MFsPM=0;}

if(ddv3in <= RR){ddv3MFsPL=0;} / Check if dv3in is in PL interval

else if (ddv3in > RR && ddv3in <= SS){ddv3MFsPL=(ddv3in-RR)*(SS-RR);}

else{ddv3MFsPL=1;}

// Check Rule bases 1–9

if(dv3MFsPS>0){ / Rule bases 1-3 dv3MFsPS >0

if(ddv3MFsPS>0){

/ 1st Rule base

if(dv3MFsPS<ddv3MFsPS){

if(NF3>=dv3MFsPS){NF3=NF3;}

else{NF3=dv3MFsPS;}

}else{

if(NF3>=ddv3MFsPS){NF3=NF3;}

else{NF3=ddv3MFsPS;}

}

}

if(ddv3MFsPM>0){

/ 2nd Rule base

if(dv3MFsPS<ddv3MFsPM){

if(NF3>=dv3MFsPS){NF3=NF3;}

else{NF3=dv3MFsPS;}

}else{

if(NF3>=ddv3MFsPM){NF3=NF3;}

else{NF3=ddv3MFsPM;}

}

}

if(ddv3MFsPL>0){

/ 3rd Rule base

if(dv3MFsPS<ddv3MFsPL){

if(NF3>=dv3MFsPS){NF3=NF3;}

else{NF3=dv3MFsPS;}

}else{

if(NF3>=ddv3MFsPL){NF3=NF3;}

else{NF3=ddv3MFsPL;}

}

```

```

}

}

if(dv3MFsPM>0){ / Rule bases 4-6 dv3MFsPM >0

if(ddv3MFsPS>0){

/ 4th Rule base

if(dv3MFsPM<ddv3MFsPS){

if(ZF3>=dv3MFsPM){ZF3=ZF3;}

else{ZF3=dv3MFsPM;}

}else{

if(ZF3 >= ddv3MFsPS){ZF3 = ZF3;}

else{ZF3=ddv3MFsPS;}

}

if(ddv3MFsPM>0){

/ 5th Rule base

if(dv3MFsPM<ddv3MFsPM){

if(PF3>=dv3MFsPM){PF3=PF3;}

else{PF3=dv3MFsPM;}

}else{

if(PF3>=ddv3MFsPM){PF3=PF3;}

else{PF3=ddv3MFsPM;}

}

}

if(ddv3MFsPL>0){

/ 6th Rule base

if(dv3MFsPM<ddv3MFsPL){

if(ZF3>=dv3MFsPM){ZF3=ZF3;}

else{ZF3=dv3MFsPM;}

}else{

if(ZF3 >= ddv3MFsPL){ZF3 = ZF3;}

else{ZF3=ddv3MFsPL;}

}

}

}

if(dv3MFsPL>0){ / Rule bases 7-9 dv3MFsPL >0

if(ddv3MFsPS>0){

/ 7th Rule base

if(dv3MFsPL<ddv3MFsPS){

if(NF3>=dv3MFsPL){NF3=NF3;}

```

```

else{NF3=dv3MFsPL;}

}else{

if(NF3>=ddv3MFsPS){NF3=NF3;}

else{NF3=ddv3MFsPS;}

}

}

if(ddv3MFsPM>0){

/ 8th Rule base

if(dv3MFsPL<ddv3MFsPM){

if(NF3>=dv3MFsPL){NF3=NF3;}

else{NF3=dv3MFsPL;}

}else{

if(NF3>=ddv3MFsPM){NF3=NF3;}

else{NF3=ddv3MFsPM;}

}

}

if(ddv3MFsPL>0){

/ 9th Rule base

if(dv3MFsPL<ddv3MFsPL){

if(NF3>=dv3MFsPL){NF3=NF3;}

else{NF3=dv3MFsPL;}

}else{

if(NF3>=ddv3MFsPL){NF3=NF3;}

else{NF3=ddv3MFsPL;}

}

}

}

deltaFD3=(NF3*VNF3+ZF3*VZF3+PF3*VPF3)/(NF3+ZF3+PF3);

FD3=FD3+deltaFD3;

if(FD3 < 0){FD3=0;}

if(FD3/FLD3 > 1 \&\& FS1==0 \&\& FS2==0){FS3=1;}

else{FS3=0;}

FDSW1[t]=FS1, FDSW2[t]=FS2, FDSW3[t]=FS3;

}return;

```

# ภาคผนวก ง

การเปรียบเทียบผลจำลองสถานการณ์วงจรแปลงผันกำลังไฟฟ้าแบบบูสต์ เรียงต่อกันสามขั้น เมื่อกระบวนการควบคุมฟัซซีมีการเปลี่ยนแปลง

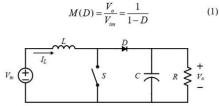

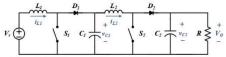

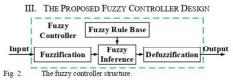

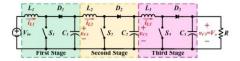

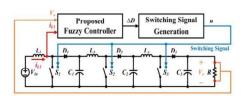

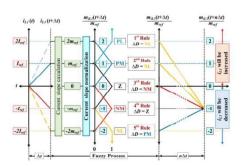

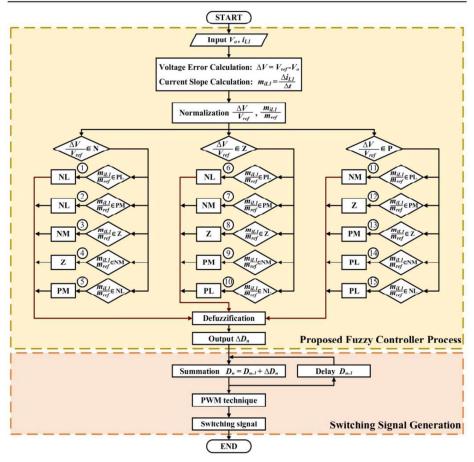

กระบวนการควบคุมพีซซีประกอบด้วยสองส่วนประกอบด้วยส่วนที่หนึ่งคือการการประเมิน ค่าของตัวแปรที่ได้ในกฎของฟัซซี (Fuzzy rule evaluation) จะเป็นขั้นตอนถัดไปหลังจากคำนวณหา ค่าระดับความเป็นสมาชิกของอินพุตทั้งหมด ซึ่งจะเป็นส่วน IF จุดประสงค์เพื่อทำการประเมินว่าค่า เงื่อนไขจากอินพุตนั้นจะทำให้กฎใดต้องกระทำในส่วน THEN ต่อไป ซึ่งอาจจะมีกฎในเงื่อนไขดังกล่าว มากกว่าหนึ่งกฎพร้อม ๆ กัน เนื่องมาจากมีอินพุตมากกว่าหนึ่ง เงื่อนไขของแต่ละอินพุตจะถูกประเมิน ค่าด้วยตัวกระทำของฟัซซีเซต เพื่อให้ได้ผลลัพธ์สุดท้ายเป็นค่าตัวเลขที่สามารถนำไปประเมินค่าส่วน THEN ซึ่งภายหลังจะถูกนำไปประเมินเพื่อหาค่าระดับความเป็นสมาชิกของตัวแปรเอาต์พุตในขั้นตอน ต่อไป ส่วนที่สองคือการรวมกฎ (Aggregation) เป็นกระบวนการหลังจากฎต่าง ๆ ถูกประเมินค่าแล้ว กฎที่มีผลไม่เท่ากับศูนย์จะถูกรวมเข้าด้วยกันโดยการรวมผลลัพธ์ของฟังก์ชันสมาชิกที่ผ่านการประเมิน ค่า หรือปรับขนาดทั้งหมดเข้าด้วยกันเป็นเซตเดียวสำหรับแต่ละตัวแปรเอาต์พุต การรวมกฎจะใช้ตัว กระทำยูเนียน ในขั้นตอนต่อไปการเปรียบเทียบผลจำลองสถานการณ์วงจรแปลงผันกำลังไฟฟ้า แบบบูสต์เรียงต่อกันสามขั้น เมื่อกระบวนการควบคุมพัซซีมีการเปลี่ยนแปลง ประกอบด้วยการจำลอง สถานการณ์วงจรแปลงผันกำลังไฟฟ้าแบบบูสต์เรียงต่อกันสามขั้นภายใต้การควบคุมพีซซีที่มีการ เปลี่ยนแปลงจำนวนกฎของพีซซี การจำลองสถานการณ์วงจรแปลงผันกำลังไฟฟ้าแบบบูสต์เรียงต่อกัน สามขั้นภายใต้การควบคุมพีซซีที่มีการเปลี่ยนแปลงขอบเขตของสมาชิกฟังก์ชัน และการจำลอง สถานการณ์วงจรแปลงผันกำลังไฟฟ้าแบบบูสต์เรียงต่อกันสามขั้นภายใต้การควบคุมฟัซซีที่มีการ เปลี่ยนแปลงรูปทรงของฟังก์ชันสมาชิกของวิธีการตรวจจับความผิดพร่องที่สวิตช์ตัวที่ 2

# การจำลองสถานการณ์วงจรแปลงผันกำลังไฟฟ้าแบบบูสต์เรียงต่อกันสามขั้นภายใต้การควบคุม ฟัซซีที่มีการลดจำนวนกฎของฟัซซี

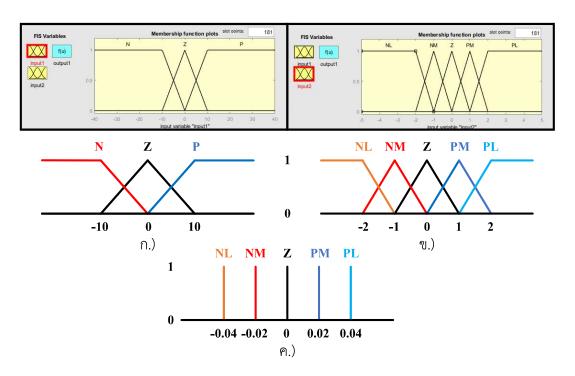

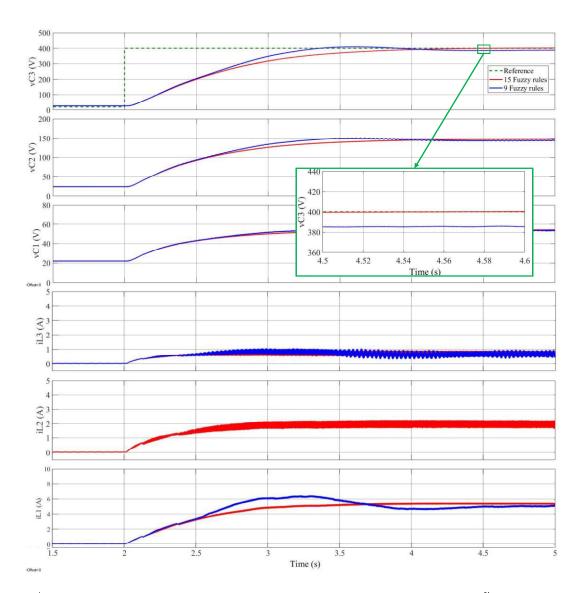

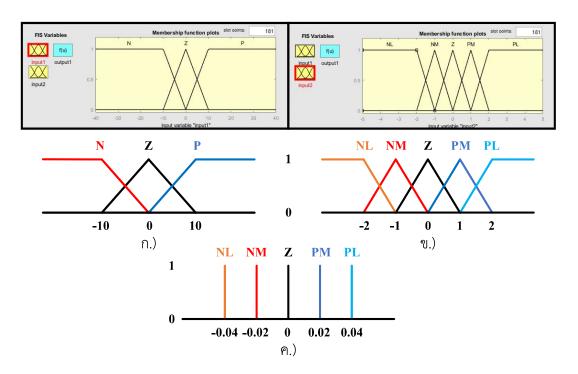

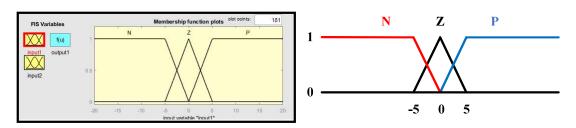

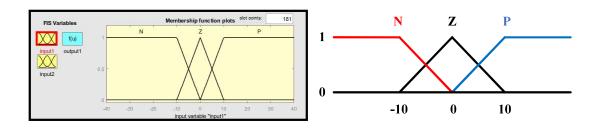

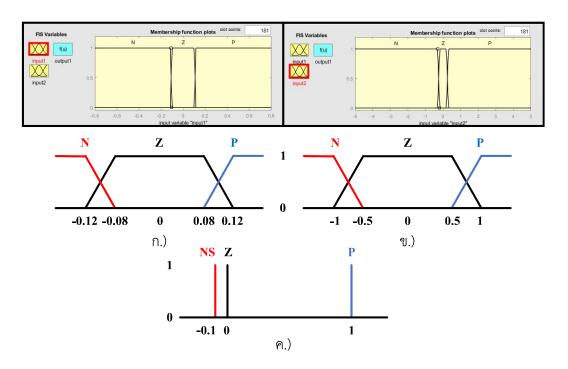

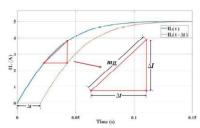

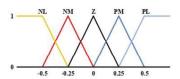

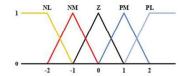

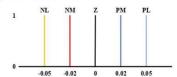

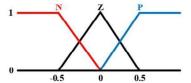

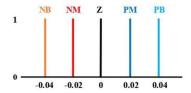

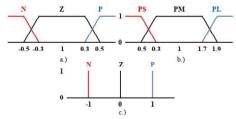

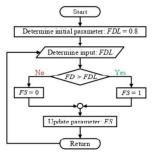

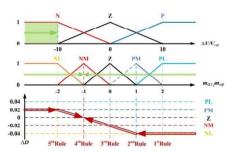

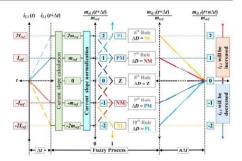

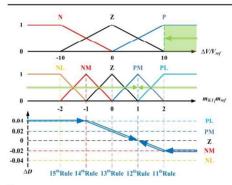

ในการแสดงการเปรียบเทียบการจำลองสถานการณ์วงจรแปลงผันกำลังไฟฟ้าแบบบูสต์เรียง ต่อกันสามขั้นภายใต้การควบคุมฟัชซีที่มีการเปลี่ยนแปลงจำนวนกฎของฟัชซี โดยการลดจำนวน สมาชิกฟังก์ชันของ  $m_{i\!L\,1}/m_{r\!e\!f}$  จาก 5 เซต เป็น 3 เซต แต่ยังคงจำนวนสมาชิกฟังก์ชันของเอาต์พุต  $\Delta D$  ไว้ที่ 5 เซตเช่นเดิม โดยสมาชิกฟังก์ชันเดิม และสมาชิกฟังก์ชันใหม่ที่เพิ่มขึ้นแสดงดังรูปที่ ง.1 และ ง.2 ตามลำดับ

รูปที่ ง.1 สมาชิกฟังก์ชันเดิม ก.)  $\Delta V_{O}/V_{ref}$  ข.)  $m_{iL1}/m_{ref}$  และ ค.)  $\Delta D$

รูปที่ ง.2 สมาชิกฟังก์ชันใหม่ ก.)  $\Delta V_{o}/V_{ref}$  ข.)  $m_{i\!L1}/m_{ref}$  และ ค.)  $\Delta D$

จากการเพิ่มขึ้นของสมาชิกฟังก์ชันของ  $m_{i L 1}/m_{ref}$  ส่งผลให้จำนวนกฎของฟัซซีลดลงนจาก 15 กฎ เป็น 9 กฎ โดยการออกแบบกฎของฟัซซีจะอ้างอิงจากการออกแบบเดิมดังนี้

1st IF

$$\Delta V/V_{ref} = N$$

AND  $m_{iL1}/m_{ref} = PM$  THEN  $\Delta D = NL$

2nd IF  $\Delta V/V_{ref} = N$  AND  $m_{iL1}/m_{ref} = Z$  THEN  $\Delta D = NM$

3rd IF  $\Delta V/V_{ref} = N$  AND  $m_{iL1}/m_{ref} = NM$  THEN  $\Delta D = NM$

4th IF  $\Delta V/V_{ref} = Z$  AND  $m_{iL1}/m_{ref} = PM$  THEN  $\Delta D = NM$

5th IF  $\Delta V/V_{ref} = Z$  AND  $m_{iL1}/m_{ref} = Z$  THEN  $\Delta D = Z$

6th IF  $\Delta V/V_{ref} = Z$  AND  $m_{iL1}/m_{ref} = NM$  THEN  $\Delta D = PM$

7th IF  $\Delta V/V_{ref} = P$  AND  $m_{iL1}/m_{ref} = PM$  THEN  $\Delta D = Z$

8th IF  $\Delta V/V_{ref} = P$  AND  $m_{iL1}/m_{ref} = Z$  THEN  $\Delta D = PM$

9th IF  $\Delta V/V_{ref} = P$  AND  $m_{iL1}/m_{ref} = Z$  THEN  $\Delta D = PM$

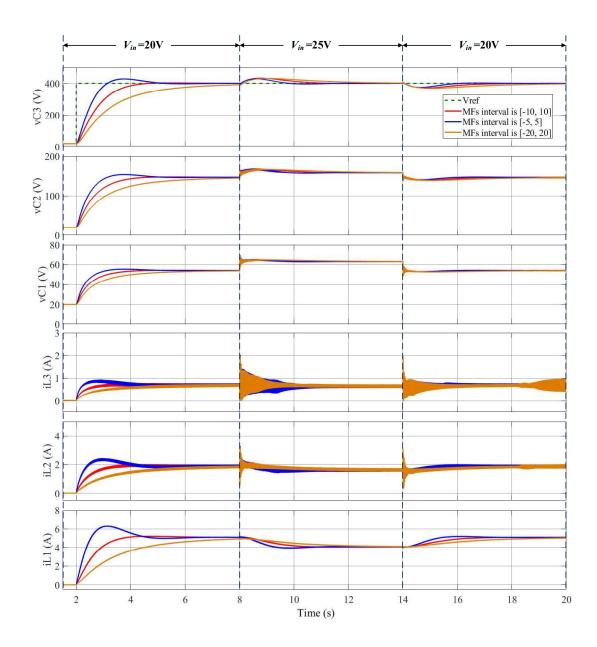

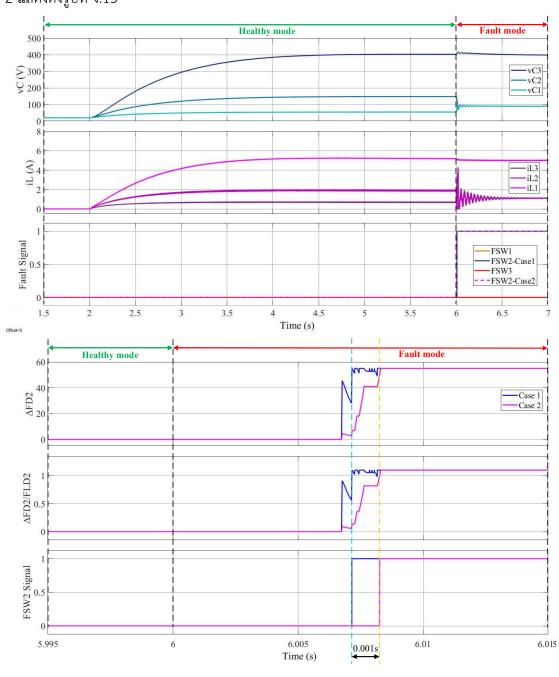

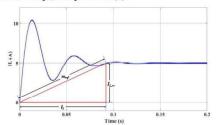

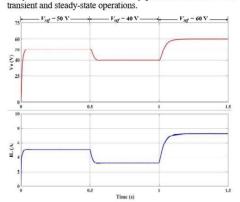

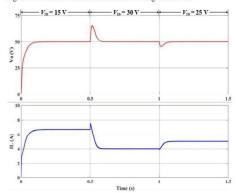

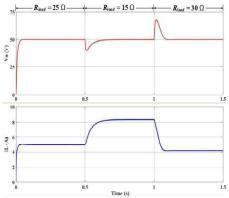

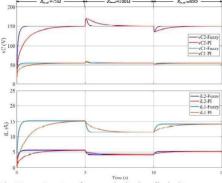

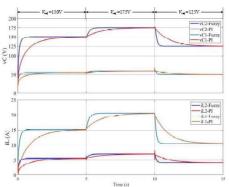

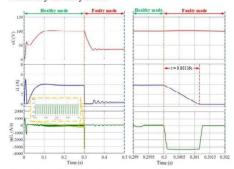

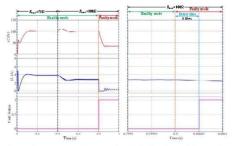

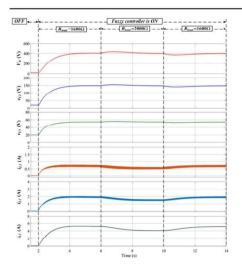

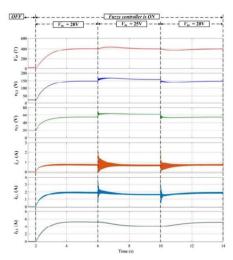

จากการออกแบบการควบคุมพีซซีเดิม และการควบคุมพีซซีที่ลดจำนวนกฎ สามารถยืนยัน ประสิทธิผล และเปรียบเทียบสมรรถนะด้วยการจำลองสถานการณ์วงจรแปลงผันกำลังไฟฟ้าแบบบูสต์ เรียงต่อกันสามขั้นภายใต้สภาวะการทำงานเดียวกัน ผลการจำลองสถานการณ์ในสภาวะปกติแสดงดัง รูปที่ ง.3 โดยการจำลองสถานการณ์เปรียบเทียบสมรรถนะในสภาวะการทำงานปกติโดยที่แรงดัน  $V_{ref}$  มีค่าเป็น 400V แรงดัน  $V_{in}$  คงค่าที่ 20V และ R ที่ 1600 $\Omega$  แรงดันตกคร่อมตัวเก็บประจุ และกระแส ผ่านตัวเหนี่ยวนำแสดงดังรูปที่ ง.3 จะเห็นได้ว่าการควบคุมฟัซซีที่ลดจำนวนกฎฟัซซีเหลือ 9 กฎ ไม่ สามารถควบคุมการทำงานของวงจรได้อย่างถูกต้องและรวดเร็ว เมื่อเปรียบเทียบกับการควบคุมฟัซซี เดิม โดยที่สภาวะชั่วครู่ผลตอบสนองภายใต้การควบคุมฟัซซีที่ลดจำนวนกฎมีการพุ่งเกินของแรงดัน  $V_{O}$  เกินค่าแรงดัน  $V_{ref}$  อีกทั้งยังไม่สามารถควบคุมให้แรงดัน  $V_{O}$  เท่ากับแรงดัน  $V_{ref}$  ในสภาวะอยู่ ตัวอย่างเห็นได้ซัดดังที่แสดงในภาพขยาย ซึ่งการเปรียบเทียบสมรรถนะของผลตอบสนองสามารถ แสดงได้ดังตารางที่ ง.1

ตารางที่ ง.1 การเปรียบเทียบผลตอบสนองของแรงดันเอาต์พุตเมื่อมีการลดจำนวนกฎของฟัซซี

|      | จำนวน   | ผลตอบสนองของแรงดันเอาต์พุต ( $V_{\mathcal{O}}$ ) |          |               |                    |  |  |  |

|------|---------|--------------------------------------------------|----------|---------------|--------------------|--|--|--|

| กรณี | กฎฟัซซี | Rise                                             | Settling | Percent       | Steady-State Error |  |  |  |

|      |         | Time (s)                                         | Time (s) | Overshoot (%) | (%)                |  |  |  |

| 1    | 9       | 0.8                                              | 3        | 2.5           | 3.75               |  |  |  |

| 2    | 15      | 1.3                                              | 2        | 0             | 0                  |  |  |  |

รูปที่ ง.3 ผลการจำลองสถานการณ์วงจรแปลงผันกำลังไฟฟ้าแบบบูสต์เรียงต่อกันสามขั้นในสภาวะ การทำงานปกติ

# การจำลองสถานการณ์วงจรแปลงผันกำลังไฟฟ้าแบบบูสต์เรียงต่อกันสามขั้นภายใต้การควบคุม ฟัซซีที่มีการเพิ่มจำนวนกฎของฟัซซี

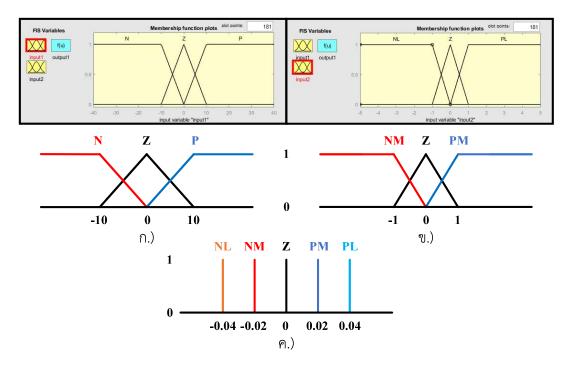

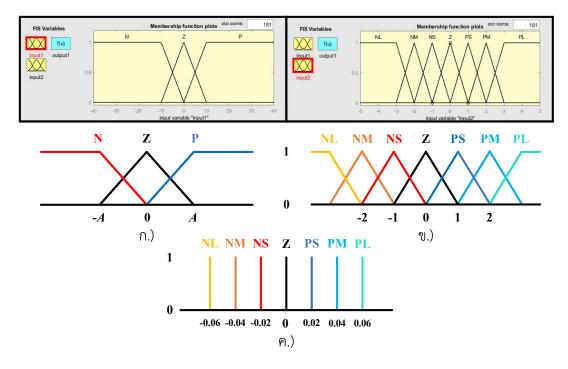

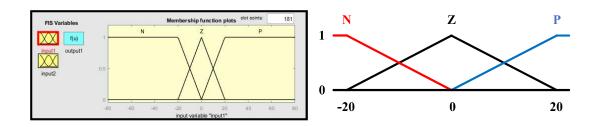

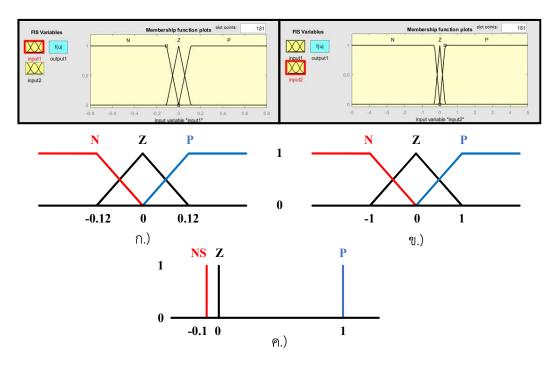

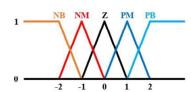

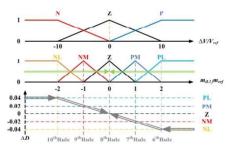

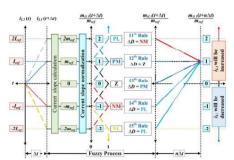

ในการแสดงการเปรียบเทียบการจำลองสถานการณ์วงจรแปลงผันกำลังไฟฟ้าแบบบูสต์เรียง ต่อกันสามขั้นภายใต้การควบคุมพืชซีที่มีการเปลี่ยนแปลงจำนวนกฎของพืชซี โดยการเพิ่มจำนวน สมาชิกฟังก์ชันของ  $m_{i,1}/m_{ref}$  จาก 5 เซต เป็น 7 เซต อีกทั้งยังเพิ่มจำนวนสมาชิกฟังก์ชันของเอาต์พุต  $\Delta D$  จาก 5 เซต เป็น 7 เซตเช่นกัน โดยสมาชิกฟังก์ชันเดิม และสมาชิกฟังก์ชันใหม่ที่เพิ่มขึ้นแสดงดัง รูปที่ ง.4 และ ง.5 ตามลำดับ

รูปที่ ง.4 สมาชิกฟังก์ชันเดิม ก.)  $\Delta V_{O}/V_{ref}$  ข.)  $m_{iL1}/m_{ref}$  และ ค.)  $\Delta D$

รูปที่ ง.5 สมาชิกฟังก์ชันใหม่ ก.)  $\Delta V_{o}/V_{ref}$  ข.)  $m_{i\!L1}/m_{ref}$  และ ค.)  $\Delta D$

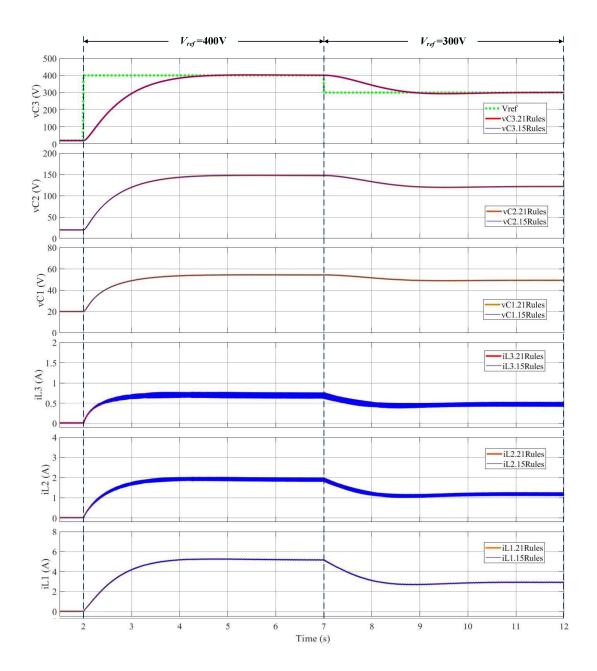

จากการเพิ่มขึ้นของสมาชิกฟังก์ชันของ  $m_{i\!L1}/m_{r\!e\!f}$  ส่งผลให้จำนวนกฎของฟัซซีเพิ่มขึ้นจาก 15 กฎ เป็น 21 กฎ โดยการออกแบบกฎของฟัซซีจะอ้างอิงจากการออกแบบเดิมดังนี้

| 1 <sup>st</sup>  | IF | $\Delta V/V_{ref} = N$ | AND | $m_{iL1}/m_{ref} = PL$ | THEN | $\Delta D = NL$ |